## SWITCHED-CAPACITOR FILTER DESIGN

by

Mohd Alauddin Bin Mohd Ali B.E., B.Sc. (enrolled as Ali Mohd Alauddin)

submitted in fulfilment of the requirements for the degree of Master of Engineering Science

UNIVERSITY OF TASMANIA

HOBART

(+0 be conferred 1984)

#### **ACKNOWLEDGEMENTS**

This work was carried out in the Electrical Engineering

Department of the University of Tasmania. The author wishes to

thank all members of the staff of the above Department for

their help and cooperation. In particular, the author

expresses his sincere appreciation to Mr. John Brodie, his

supervisor, for guidance and encouragement in the work.

Acknowledgements are also given to the Public Service

Department of Malaysia for its sponsorship and the National

University of Malaysia for its study leave award.

In the preparation of this thesis, the author thanks

Mrs. Valerie Thomas for her perseverance with the typing and

Mr. Tajul Hashim for drawing the figures.

I hereby declare that, except as stated herein, this thesis contains no material which has been accepted for the award of any other degree or diploma in any university, and that, to the best of my knowledge and belief, this thesis contains no copy or paraphrase of material previously published or written by another person except where due reference is made in the text of the thesis.

(Mohd Alauddin Bin Mohd Ali)

#### SUMMARY

The switched-capacitor (SC) technique is a very attractive method for implementing fully integrated filters in MOS technology. The filters, consisting only of switches, capacitors and operational amplifiers, can be realised through a number of design procedures. This thesis describes these design techniques and their applications.

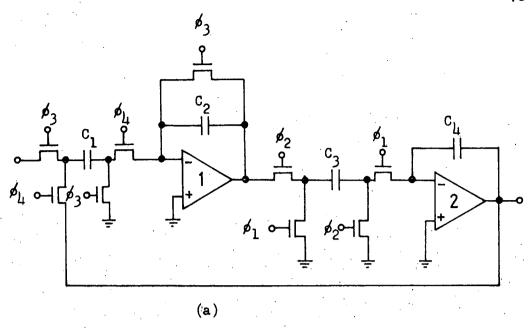

Many of the suitable designs use SC integrators which can be easily derived from the analogue active integrators. Parasitic-insensitive implementation is possible realising either the lossless discrete integrator (LDI) or the bilinear transformation. The effects of noise and other non-idealities of the switches and operational amplifiers on these integrators are described. A general biquadratic structure based on the SC integrators is given from which a circuit capable of realising bandpass transfer functions is derived. The SC biquads are cascaded or coupled for the design of higher order filters.

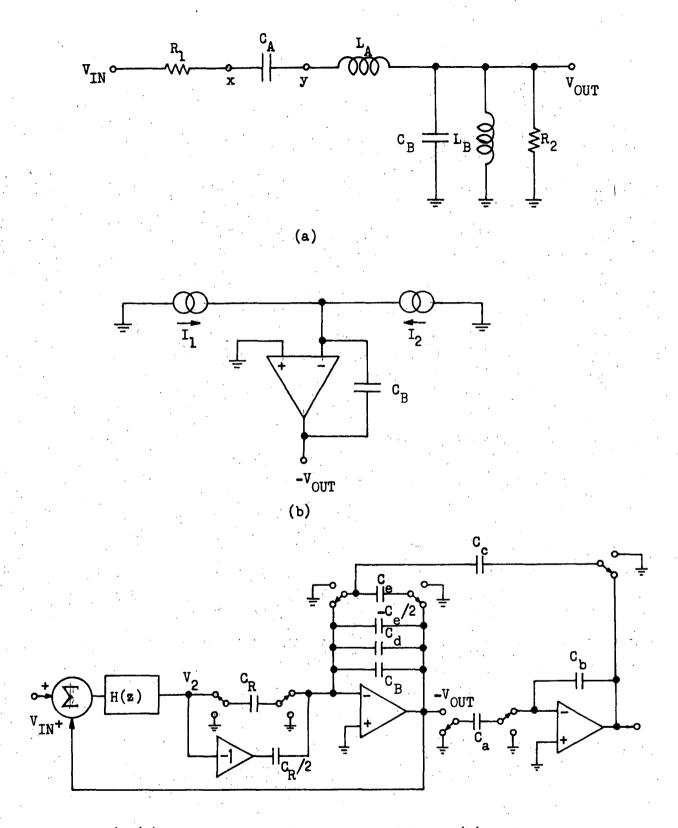

Higher order SC filters are also designed by simulating doubly-terminated LC ladder networks with integrators using the LDI transformation. Other methods of simulating the ladder network include using voltage-controlled current sources, the impedance simulation method and voltage inverter switches. These methods mostly produce circuits which are sensitive to parasitic capacitances and are only briefly described.

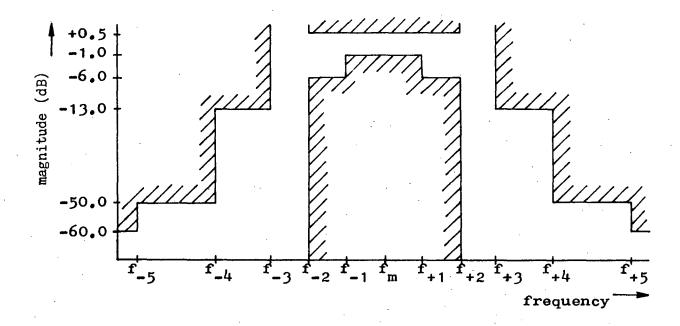

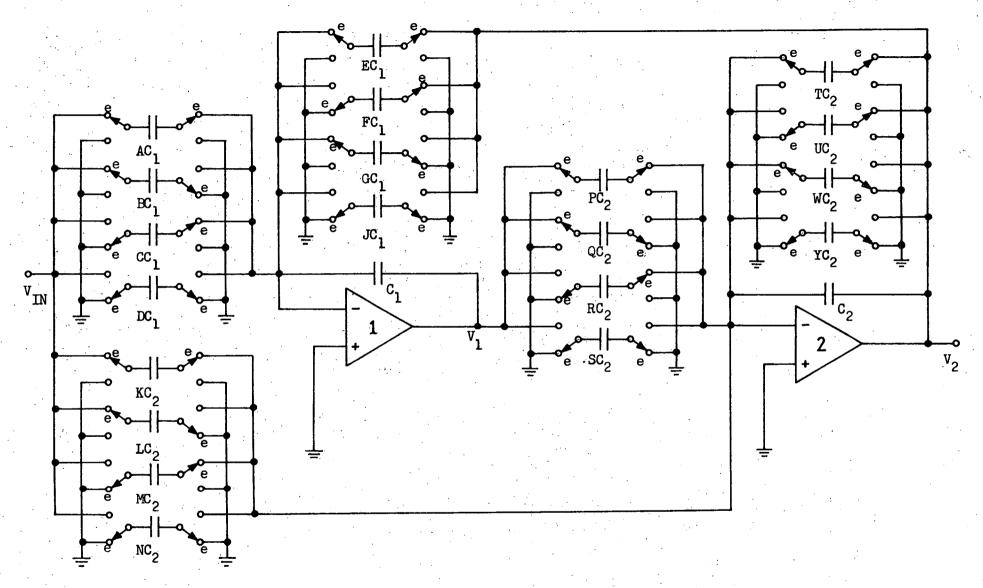

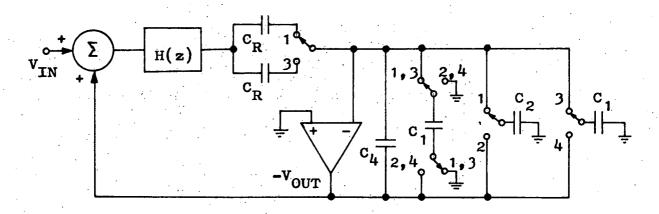

These design techniques are used to design SC filters which meet the one-third octave bandpass filter specification required for the analysis of acoustic noise and vibration. The midband frequencies of the resulting SC bandpass filters can be varied from 10Hz to 20kHz. The designs are made using clock frequency at a minimum value possible and another at 48 times the midband frequency. The suitable circuits are compared with regard to their requirements and performances.

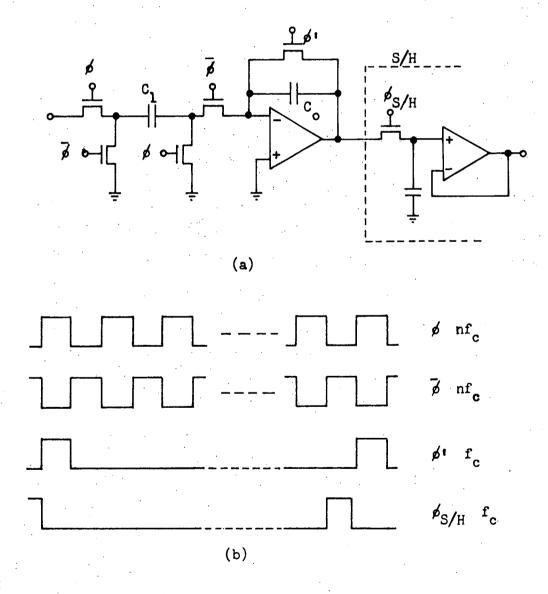

The antialiasing problem due to the wide range of required midband frequencies is overcome with the use of an SC decimator circuit. This allows the antialiasing filter, the decimator and other accessories to be implemented on a single chip with the SC bandpass filter.

The SC circuits are analysed using their z-transform relations. The nodal analysis technique and the equivalent circuit method are described and used for deriving z-transform transfer functions of the SC filters. These are then used to predict the frequency responses of the filters and their sensitivity as to variation of one single capacitor value.

# CONTENTS

| CHAPTER C | )N | ΙE |

|-----------|----|----|

|-----------|----|----|

| INTRODUCTION                                        | 1  |

|-----------------------------------------------------|----|

| 1.1 Switched-capacitor circuit principle            | 3  |

| 1.2 Properties of MOS components                    | 6  |

| 1.3 Practical considerations for MOS implementation | 9  |

| 1.4 Further considerations in designing             |    |

| switched-capacitor filters                          | 11 |

| REFERENCES                                          | 13 |

| CHAPTER TWO                                         |    |

| ANALYSIS OF SWITCHED-CAPACITOR NETWORKS             | 15 |

| 2.1 Analysis techniques                             | 16 |

| 2.2 Nodal analysis technique                        | 21 |

| 2.3 Equivalent circuit method                       | 25 |

| 2.4 Examples                                        | 31 |

| REFERENCES                                          | 36 |

| CHAPTER THREE                                       |    |

| SWITCHED-CAPACITOR INTEGRATORS                      | 37 |

| 3.1 Transfer functions                              | 37 |

| 3.2 Effects of parasitic capacitances               | 42 |

| 3.3 Frequency limitations                           | 45 |

| 3.4 Noise considerations                            | 5  |

| 3.5 Damped switched-capacitor integrators           | 51 |

| 3.6 Summary                                         | 6  |

| DEFEDENCES                                          | 6: |

## CHAPTER FOUR

| DESIGN OF SWITCHED-CAPACITOR BANDPASS FILTER         | 64  |

|------------------------------------------------------|-----|

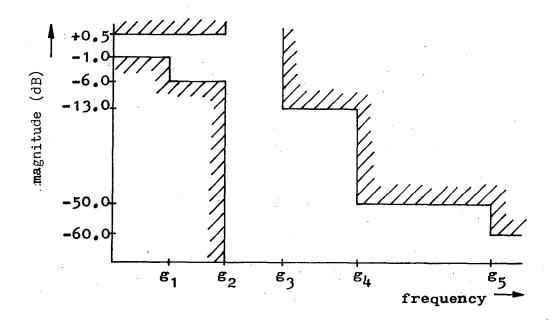

| 4.1 Specification of the bandpass filter             | 64  |

| 4.2 Transfer function satisfying the specification   | 66  |

| 4.3 Transfer function satisfying the bilinearly-     |     |

| prewarped specification                              | 69  |

| 4.4 Transfer function satisfying the LDI-            | •   |

| prewarped specification                              | 71  |

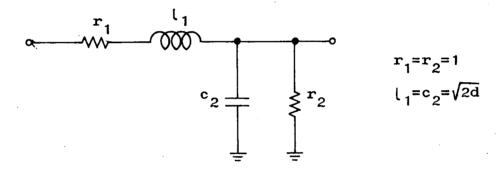

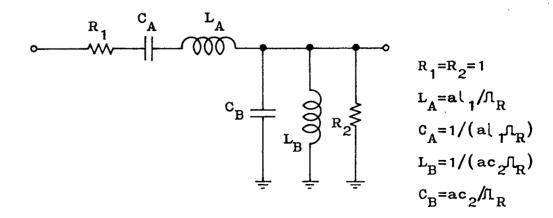

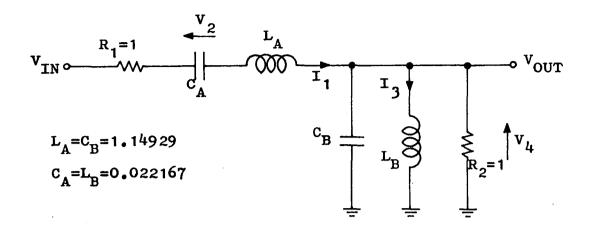

| 4.5 Ladder network satisfying the specification      | 73  |

| REFERENCES                                           | 74  |

| CHAPTER FIVE                                         | ·   |

| SWITCHED-CAPACITOR BIQUADS                           | 75  |

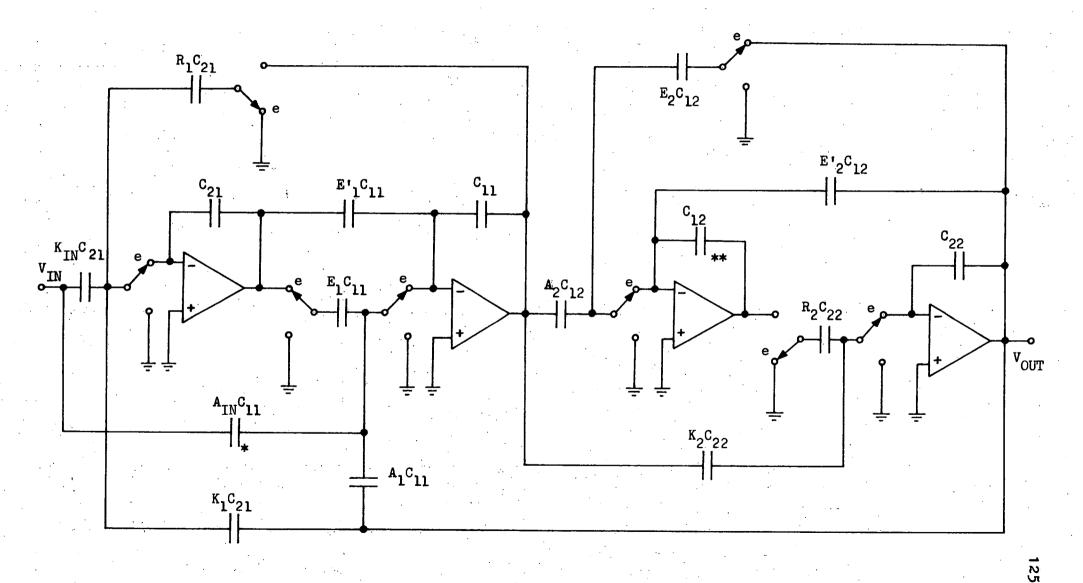

| 5.1 General biquadratic structure                    | 76  |

| 5.2 Transfer functions of the general biquad         | 82  |

| 5.3 Derivation from the general biquad               | 85  |

| 5.4 Design using the bilinear transformation         | 89  |

| 5.5 Design by matching transfer functions            | 91  |

| 5.6 Design example using the bilinear transformation | 92  |

| 5.7 Realising sections with optimum pole-zero        |     |

| pairing                                              | 98  |

| 5.8 Design examples by matching transfer functions   | 101 |

| 5.9 Summary                                          | 105 |

| REFERENCES                                           | 108 |

| CHAPTER SIX                                          |     |

| SWITCHED-CAPACITOR LADDER FILTERS                    | 109 |

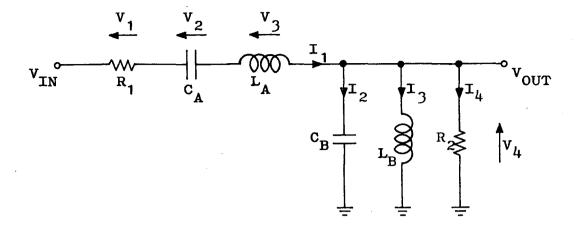

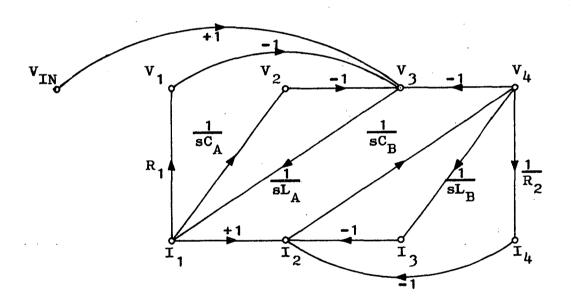

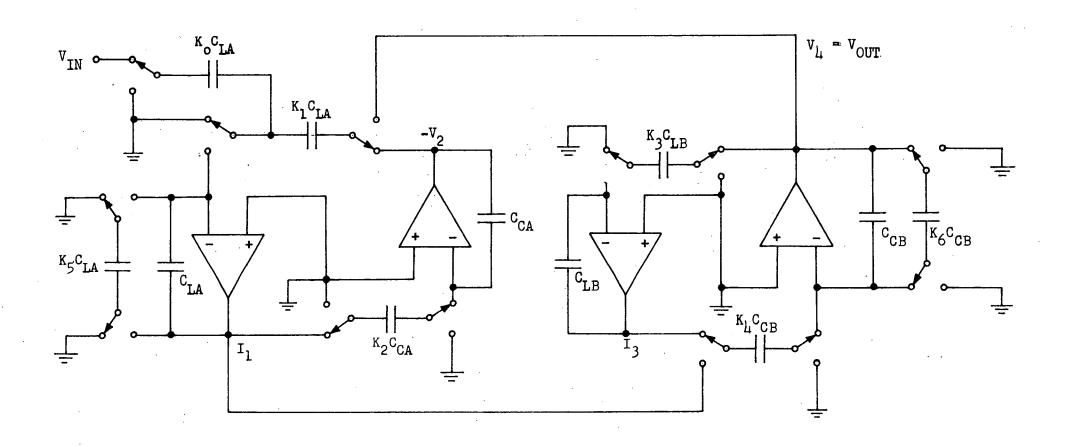

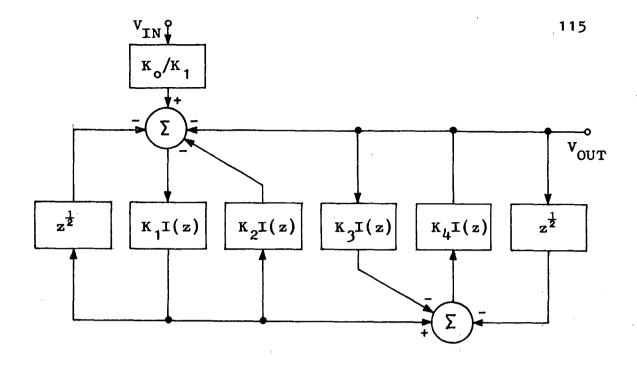

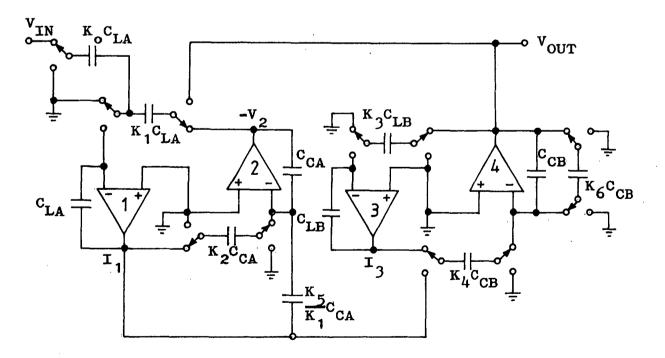

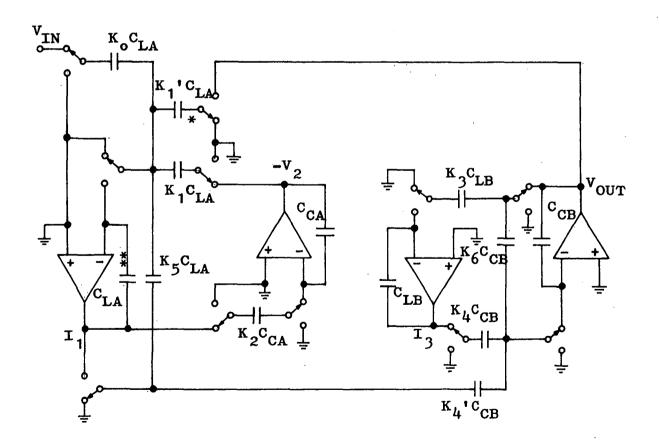

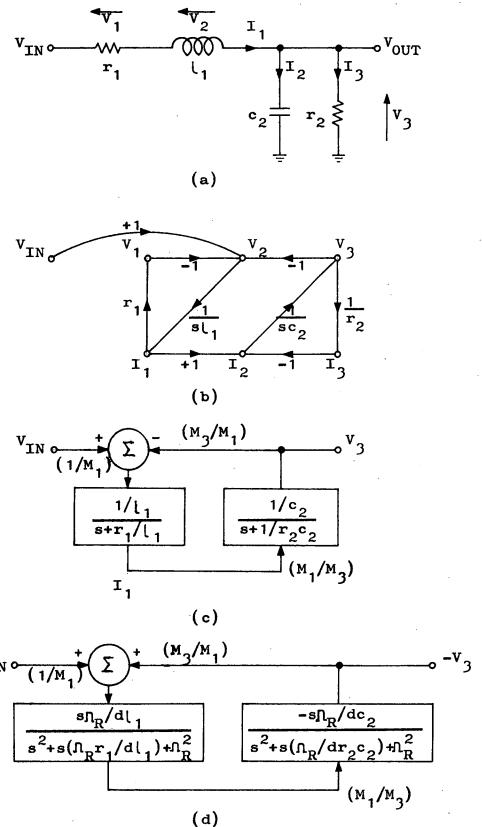

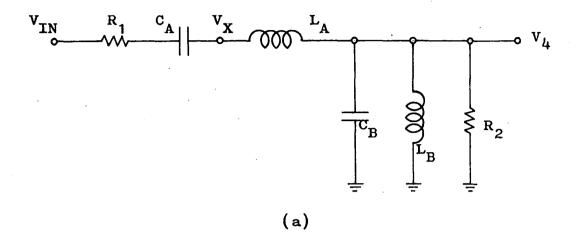

| 6.1 Design using LDI transformation                  | 109 |

| 113             |

|-----------------|

| •               |

| 116             |

|                 |

| 116             |

| 117             |

| ype 121         |

|                 |

| 126             |

| 1 29            |

| *               |

|                 |

| 130             |

| 130             |

| s 13!           |

| 137             |

| 14              |

| 147             |

| 15              |

| 15 <sup>1</sup> |

|                 |

| 150             |

| 156             |

| 16              |

| 16              |

| 16              |

|                 |

|         |              |             |            |            |     | , , , |

|---------|--------------|-------------|------------|------------|-----|-------|

| REI     | FERENCES     |             |            |            |     | 170   |

|         |              |             |            |            |     |       |

|         |              |             |            |            |     |       |

| APPEND  | IX A         | •           | v.         |            | *   |       |

| Tra     | ansfer Func  | tion of Swi | .tched-Cap | acitor     |     | • .   |

| In      | tegrator wit | th Finite ( | perationa  | 1 Amplifie | er  |       |

| Baı     | ndwidth      |             |            |            |     | 171   |

|         |              |             |            |            | * * |       |

| BTBI TO | LD V DILA    |             | **         | • .        |     | 175   |

#### CHAPTER ONE

#### INTRODUCTION

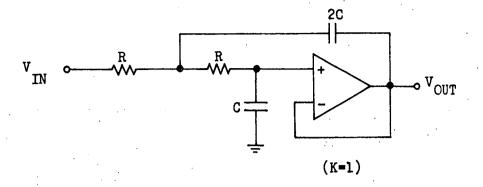

Filters for frequency selective filtering are among the most common circuits in electronic systems. With the advent of integrated circuit technology, it has also been desirable to produce filters in monolithic form. Towards this end, filters have been successfully reduced in size and cost with the replacement of RLC networks by active-RC circuits. Avoiding the bulky and costly inductors, thin-film resistors and capacitors can be realised with silicon integrated circuit operational amplifiers. This hybrid integrated circuit can be fitted into a small 16-pin dual-in-line package.

Further reduction by realising resistors and capacitors on the silicon chip together with the operational amplifier (OA) transistors has been found to be unsuitable for implementing precision filters. In order to define accurately the RC product, the absolute values of R and C have to be well controlled which are difficult in current integrated circuit (IC) technology. Integrated resistors have poor linearity and temperature characteristics and they do not track with those of the capacitors on the same chip. However, tracking in variations of the same components allows the possibility of defining resistor or capacitor ratios accurately. Active-R filters have been implemented, which use the OA as integrators with their filter parameters established via resistor ratios.[1]

In metal-oxide-semiconductor (MOS) technology, however, it is more accurate to implement capacitor ratios since high quality capacitors can be conveniently realised in MOS IC. Furthermore, they are less prone to drift and use less silicon area than resistor ratios. Thus active-C filters, which are readily obtained by replacing the resistors in active-R filters

with capacitors, provide a better possibility for full integration of analogue filters.[2]

Another approach for full integration of filters has also been possible due to accurate capacitor ratios and another unique property of MOS IC. The MOS IC offers the ability to store charge on a node for several milliseconds and to sense this stored charge continuously and non-destructively. This feature enables the implementation of analogue sampled-data filters such as the bucket brigade filters [3], the charge-coupled device (CCD) filters [4], the direct-form recursive filters [5] and the switched-capacitor filters (SCFs).[6]

Thus a number of ways have been attempted for the reduction in size and cost of filters. Among these, the switched-capacitor (SC) technique seems to be the most attractive for the implementation of precise fully integrated filters especially in the voice-frequency range. The SCF consists only of capacitors, OAs and analogue switches which are all easily implemented in MOS IC. The filter parameters are determined by capacitor ratios and the frequency at which the switches are clocked. The input signal to the SCF is sampled in time thus it should be bandlimited as dictated by the sampling theorem. Hence an antialiasing filter is required. However, a simple continuous-time filter with no stringent requirement can be easily implemented on the same chip and is usually sufficient for this purpose.

Fully integrated filters have now been implemented in a number of applications using the SC technique. Transmit and Receive Filters for a Pulse-code-modulation (PCM) coder-decoder (CODEC) system have been fabricated together with the CODEC and other interface circuits on the same chip.[7] A Dual Tone Multifrequency (DTMF) receiver can now be

fabricated on a single chip including all its required filter circuits.[8]

Programmable SCFs with applications such as in adaptive filters, and

speech and music synthesisers, can also be easily implemented due to the

filter parameter dependence only on capacitor ratios and clock frequency.[9]

The parameter dependence on the clock frequency allows the possibility of implementing an integrated bandpass filter with fixed capacitor ratios but having its centre frequency tracking the clock frequency. This SC bandpass filter may then be used in applications such as in acoustic noise measurement which involves measuring the level of noise components in different bands of the audio spectrum.[10] The different filters required from the set are obtained by only adjusting the clock frequency of the SC bandpass filter instead of altering the component values as had to be done when using active-RC filters.

This thesis describes the development in SCF designs, their advantages and limitations when compared to active-RC filters or other ways of implementing monolithic filters. A number of techniques have been proposed for the design of SCFs.[11] These techniques are described and applied here for the design of the bandpass filter required for acoustic noise measurement. The requirements and performance of the resulting SCFs are then compared to determine their suitability for integrated circuit implementation.

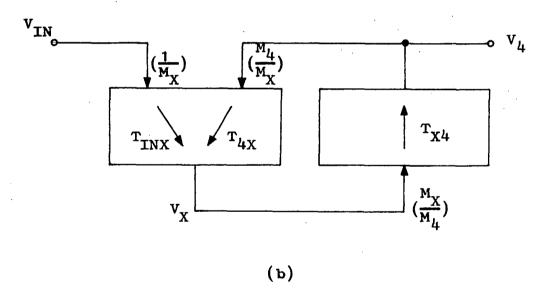

## 1.1 Switched-capacitor circuit principle

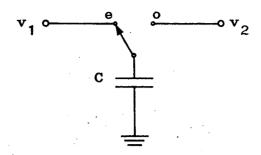

The above discussions have shown that in order to implement filters in MOS technology, it is desirable for resistors to be avoided. In switched-capacitor (SC) technique, the resistors are replaced by utilising capacitors and switches. Current flow in resistors is simulated by charge transfer

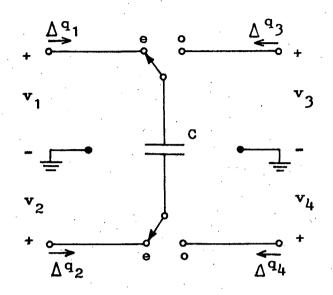

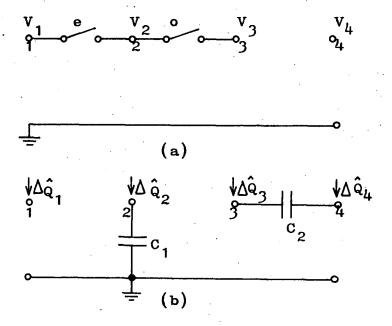

on rapidly switched capacitors. This can be illustrated by the switched-capacitor circuit in fig. 1:1.

Assume the switch is initially at position e, then the capacitor C is charged to voltage  $v_1$ . When the switch is thrown to position o, the capacitor C is discharged (or charged) to voltage  $v_2$ . The amount of charge that flows into (or from) the voltage source  $v_2$  is  $C(v_1 - v_2)$ . If the switch is thrown back and forth every T seconds, then the current flow, on the average, is

$$i = \frac{C(v_1 - v_2)}{T}$$

(1:1)

If the switching rate,  $f_c = \frac{1}{T}$  is much larger than the signal frequencies of interest, the sampling time of the signal which occurs in the circuit of fig. 1:1 can be ignored, thus the circuit is equivalent to a resistor of value

$$R = T/C = 1/(f_cC)$$

(1:2)

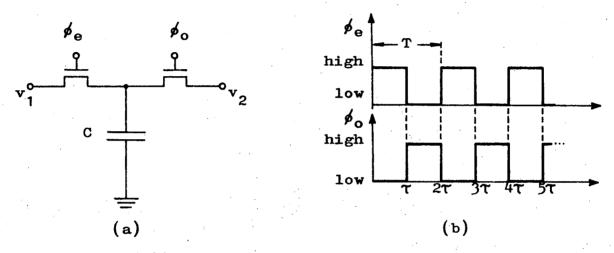

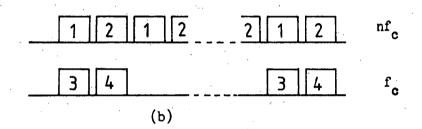

The MOS implementation of the SC circuit in fig. 1:1 is given in fig. 1:2(a). The two MOSFETs are operated as ideal switches which are controlled by a two-phase non-overlapping clock at the frequency, fc as shown in fig. 1:2(b). The even (e) and odd (o) clock phases, denoted by  $\phi_e$  and  $\phi_o$  respectively, close the switches when they are high. In practice, slightly less than 50% duty cycle is required to ensure the two switches never close simultaneously. However, for simplicity, 50% duty cycle is assumed in subsequent analyses of biphase SCFs.

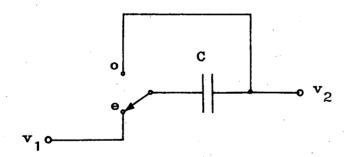

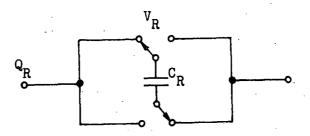

The SC circuit shown in fig. 1:3 also simulates a resistor as in (1:2). These circuits can thus replace resistors in any active-RC filters to form the SCFs if the assumptions in the above illustration are all satisfied. [12] [13]

Fig. 1:1 A switched-capacitor circuit simulating a resistor.

Fig. 1:2 (a) An MOS implementation of circuit in fig. 1:1.

(b) Timing diagram.

Fig. 1:3 A series switched-capacitor.

Inductors can also be simulated using the simulated resistors, capacitors and OAs, hence passive filter response can also be obtained by an SCF.

There are, however, a number of other considerations to be taken into account to ensure that high performance filters are achieved. These are discussed in detail in the following sections.

## 1.2 Properties of MOS components

As have been mentioned, it is relatively easy to implement capacitors, switches and OAs in the MOS technology. These high quality MOS elements have made the implementation of precise SCF possible. However certain properties of these components do impose some limitations on the range of realisable filters. In this section the properties of these components, produced through the CMOS or NMOS processes, are described.

#### (a) MOS capacitors

In the NMOS and CMOS processes, capacitor plates can be made of metal (usually aluminium), or polycrystalline silicon (polysilicon), or heavily-doped crystalline silicon. For examples, a heavily doped region in the silicon substrate can be made the bottom plate with the interconnect metallisation made the top plate or both plates can be formed by two polysilicon layers. These materials are very conductive. The dielectric material is SiO<sub>2</sub>, an excellent insulator, which can be thermally grown from the silicon layer. These capacitors exhibit good ratio accuracy and low voltage and temperature coefficients.

The value of the capacitors is determined by the dielectric constant, the thickness of the dielectric and the area of the capacitor. Assuming that the dielectric constant and thickness do not vary, the ratio of two capacitors, made within the same integrated circuit, will depend only on

their area ratio. This is primarily determined by the geometrical shape of the capacitors defined by the photolithographic mask used to make the integrated circuit.

Error in the ratio can thus result from uncertainties in the photolithographic edge definition. The possible variation of the dielectric thickness with distance across the integrated circuit can also contribute to errors. These effects can be overcome by careful layout of the components. The errors generally get smaller as the capacitor dimensions are made larger. The achievable ratio accuracies range from 1-2% for small capacitor geometries ( $\sim 400 \, \mu m^2$ ) to about 0.1% for capacitor geometries which approach the limit of economical size  $(40,000 \, \mu m^2)$ .[6] This implies that as the capacitor ratio increases the accuracy decreases since the smaller of the two capacitors must be decreasing.

Voltage coefficients of MOS capacitors are in the range of 10 to 100 ppm/V. Temperature coefficients are generally in the range of 20 to 50 ppm/°C. These variations are much lower for the value of a ratio and can be considered insignificant in almost all applications.

The manner in which the capacitor is constructed, as described above, renders parasitic capacitance unavoidable. The bottom plate, which is in the substrate or close to it, is coupled to the substrate by a parasitic capacitance with a value of 5 to 20% of the MOS capacitor itself. The interconnecting lines connected to the top plate causes a parasitic capacitance to be present from the top plate to the substrate. This has a value ranging from 0.1 to 5% of the capacitor. Hence sizeable parasitic capacitances are present and they are non-linear, thus, cannot be neglected if high performance filters are required. [6]

#### (b) MOS switches

The MOS transistors can operate as good switches. When the transistor is in the off-mode, the off-resistance is, for practical purposes, infinite. The on-resistance depends on the area allowed for the MOS transistor. In NMOS silicon gate technology, switch device with a channel length of  $5\mu m$  can be achieved. In this case, for a width-to-length ratio of unity, the on-resistance is  $5k\Omega$  if the gate drive voltage is 5V with respect to the source. However, in a larger area,  $1k\Omega$  on-resistance can readily be attained.

The 5µm device has a leakage current from source and drain to substrate on the order of 10<sup>-14</sup>A at 70°C. The parasitic capacitances from source and drain to substrate is about 0.020pF each. The overlap capacitance from drain to gate and source to gate is about 0.005pF. The charge induced in the channel, when the gate potential is 5V more positive than the source and drain, is approximately 0.03pC.[6] These properties need to be considered in applications where the switches cannot be assumed ideal.

#### (c) MOS operational amplifiers

The recent trend towards higher level of integration on MOS Large Scale Integration (LSI) chips has led to considerable works being done in realising CMOS and NMOS OAs. A number of high performance OAs have been designed to date. Operational Amplifiers with up to 90dB open loop gain, unity-gain bandwidth of 10MHz or power dissipation of 2mW are now practical. [11][17]

Typical values, which are easily achievable in both CMOS and NMOS technologies for OAs with ±5V supplies, are 70dB open loop gain, unity-

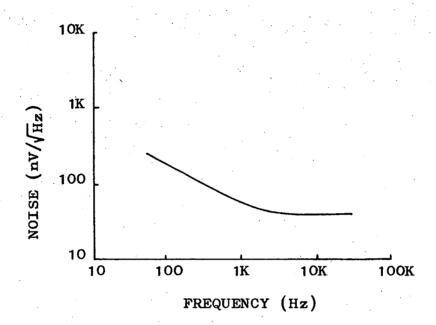

gain bandwidth of 2MHz and power dissipation of about 3 to 6 mw. The common mode and power supply rejection ratios are about 70dB. The OAs have 0.1% settling time of about  $2\mu s$  for 1 V step with a 20 pF load and slew rate of about  $3V/\mu s$ . [14][15] MOS OAs have higher offset voltage and  $^{1}/_{f}$  noise than bipolar OAs. The MOS OA dc offset is usually less than 15mv. In the overall filter, this adds up according to the filter configuration and the number of OAs used. A typical input noise versus frequency characteristic of an MOS OA is shown in fig. 1:4.[14]

The MOS OA occupies about as much space as a 50pF capacitor, that is about 0.1 to 0.2 mm<sup>2</sup> of silicon area. It does not require large capacitive and/or resistive loads driving capabilities since OAs used in SCFs are only required to drive small capacitors. Output buffer stage is, however, required for an OA to be used for driving off-chip loads.

## 1.3 Practical considerations for MOS implementation

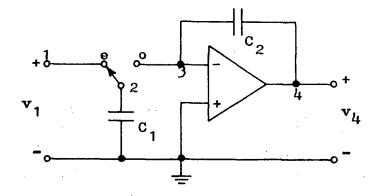

The above properties of the MOS elements placed some constraints on the type of SC networks which can be used. A number of circuit conditions have to be avoided in the MOS implementations of precision filters. The guidelines which must be observed for practical SCF configurations are listed below.

(i) Closing the OA feedback path. The OA feedback path should at least be closed by an unswitched capacitor to provide the continuous-time feedback necessary to stabilise the OA. The switched-capacitor alone cannot be used since the OA will be left open-loop during part of the clock cycle. The switched-capacitor can, however, be used in parallel with the unswitched capacitor. It can provide the dc feedback path to prevent latch-up of the OA.

(ii) No capacitor only nodes. All capacitor plates are subject to charge

Fig. 1:4 Typical input noise vs frequency characteristic of an MOS operational amplifier.

accumulation from a variety of parasitic sources. In order to insure stability of the circuit there must be a path either directly or through a switched-capacitor from every node to a voltage source or ground.

(iii) Connection of capacitor bottom plate. This plate should be connected to a voltage source/ground or switched between voltage sources/ground.

The large non-linear parasitic capacitance between this plate and the substrate will then be charged and discharged, but will not affect the filter response.

(iv) Connection of OA positive input. This input should be connected to a constant voltage. If it is connected to a signal voltage, then the filter response is sensitive to all the parasitic capacitances due to switches, bus lines and substrate that are connected to the negative input of the OA. In addition, increased common-mode performance is required of the OA. [6]

## 1.4 Further considerations in designing switched-capacitor filters

Despite the above limitations, there are still a variety of possible active filter organisations which can be used for monolithic implementation. These can be arrived at through a number of design procedures starting with an LC ladder or an active-RC filter as a model. These design approaches and the resulting SC circuits differ widely. Certain practical considerations make some of these useful networks preferable to others. The features listed below are among the considerations which can be used to compare the various SCF circuits achievable for a particular specification. [16]

- The sensitivity of the transfer function to parasitic capacitances.

- (2) The sensitivity to changes of the capacitor values, e.g. caused by fabrication inaccuracies. The tolerance scheme for the filter will

not be violated if a capacitor value, Cj lies between its upper limit, Cjmax and the lower limit, Cjmin. The value

$$\lambda = \frac{\text{Cjmax} - \text{Cjmin}}{\text{Cj}} \times 100\%$$

(1:3)

is used as a measure of the sensitivity of the filter to deviation of one single-capacitor value.

- (3) The total capacitance required which reflects on the substrate area needed.

- (4) The number of OAs in a circuit which determines the power consumption and the generation of noise. The OA is also a major factor in determining the silicon area required for an SCF.

- (5) The spread of the capacitor values which affect the accuracy of capacitor ratio definition in monolithic implementation.

- (6) The number of switches.

- (7) The number of clock phases required.

- (8) The allowable clock frequencies.

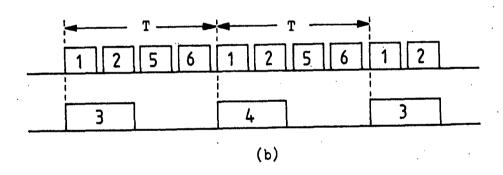

Prior to designing the filters, chapter 2 gives two basic analysis techniques which can be used for obtaining z-transform transfer functions of the SCFs. Chapter 3 deals with the SC integrators which are used in many realisable SCFs. Then the specification for the one-third octave bandpass filter is given with some preliminary design steps in chapter 4. Using this specification, SCF designs using SC biquads are done in chapter 5. Designs by simulating the doubly terminated LC ladder networks are done in chapters 6 and 7. Finally, in chapter 8, some aspects for the implementation of the SCFs are discussed.

#### REFERENCES

- [1] K. Radhakrishna Rao, S. Srinivasan, "Low-Sensitivity Active Filters using the Operational Amplifier Pole", IEEE Trans. Circuits Syst., 1974, Vol. CAS-21, pp.260-262.

- [2] R. Schaumann, J.R. Brand, "Integrable analogue active filters for implementation in MOS Technology", *IEE Proc.*, 1981, Vol. 128, Pt. G, pp.19-24.

- [3] F.L.J. Sangster, "The Bucket Brigade Delay Line, a Shift Register for analogue signals", *Philips Tech. Rev.*, 1970, Vol. 31, pp.97-110.

- [4] D.D. Buss, D.R. Collins, W.H. Bailey, C.R. Reeves, "Transversal Filtering using Charge Transfer Devices", *IEEE J. Solid State Circuits*, 1973, Vol. SC-8, pp.138-146.

- [5] I.A. Young, D.A. Hodges, "MOS Switched-Capacitor Analog Sampled-Data Direct Form Recursive Filters", *ibid.*, 1979, Vol. SC-14, pp.1020-1033.

- [6] R.W. Brodersen, P.R. Gray, D.A. Hodges, "MOS Switched-Capacitor Filters", Proc. IEEE, 1979, Vol. 67, pp.61-75.

- [7] K. Yamakido, T. Suzuki, H. Shirasu, M. Tanaka, K. Yasunari, J. Sakaguchi, S. Hagiwara, "A Single-Chip CMOS Filter/Codec", *IEEE J. Solid-State Circuits*, 1981, Vol. SC-16, pp.302-307.

- [8] B.J. White, G.M. Jacobs, G.F. Landsburg, "A Monolithic Dual Tone Multifrequency Receiver", *ibid*.1979, Vol. SC-14, pp.991-997.

- [9] D.B. Cox, L.T. Lin, R.S. Florek, H.F. Tseng, "A real-time Programmable switched-capacitor Filter", *ibid.*, 1980, Vol. SC-15, pp.972-977.

- [10] P.J. Yates, "An Investigation into the suitability of using a switched-capacitor filter to form a one-third octave B.P. filter with a variable centre frequency", Honours Thesis, Elect. Eng. Dept., University of Tasmania, 1981.

- [11] G.C. Temes, "MOS Switched-Capacitor Filters-History and the State of the Art", *Proc.*, 1981 European Conf. on Circuit Theory and Design, pp.176-185.

- [12] L.P. Huelsman, P.E. Allen, Introduction to the Theory and Design of Active Filters, New York, USA: McGraw-Hill, Inc., 1980.

- [13] M.E. Van Valkenburg, Analog Filter Design, New York, USA: Holt, Rinehart and Winston, 1982.

- [14] Y.P. Tsividis, D.L. Fraser, Jr., J.E. Dziak, "A Process-Insensitive High-Performance NMOS Operational Amplifier", *IEEE J. Solid-State Circuits*, 1980, Vol. SC-15, pp.921-928.

- [15] A. Iwata, K. Uchimura, S. Hattori, H. Shimizu, K. Ogasawara, "Low Power PCM CODEC and Filter System", *ibid.*, 1981, Vol. SC-16, pp.73-79.

- [16] E. Luder, G. Spahlinger, "Performance of various types of Switched-Capacitor Filters", Arch. Elektron. Uebertr., 1982, Vol. 36, pp.57-62.

- [17] T. Ishihara, T. Enomoto, M. Yasumoto, T. Aizawa, "High-speed NMOS Operational Amplifier Fabricated using VLSI Technology", *Electron*. *Lett.*, 1982, Vol. 18, pp.159-161.

#### CHAPTER TWO

#### ANALYSIS OF SWITCHED-CAPACITOR NETWORKS

In chapter one, it was shown that a switched-capacitor can approximate a resistor under the assumptions that the sampling frequency is much greater than the signal frequencies and that the resistor is voltage driven at both ends. In this case, the SCF can be considered equivalent to the active-RC filter it replaces and analysed as such. However, such assumptions are not always practical in the analysis of SC networks. For example, it is desirable for the signal frequencies to be as high as half the sampling frequency, thus the time delay through the switched capacitor has to be accounted for.

A more exact analysis can be obtained by applying the z-transform techniques, if the voltage sources and internal voltages of the SC networks are assumed to be sampled at times kt (where k is an integer, see fig. 1:2(b)) and held over one-half clock period. The resistor/switched-capacitor correspondence is still useful for deriving topologies of SC networks from the active-RC circuits. Then the SC networks are considered to be pure sampled-data systems and analysed using the z-transform techniques. For this analysis to be exact, the SCF has to be preceded by a sample-and-hold (S/H) stage. However, in many SC networks, this is not necessary since the S/H operations are inherently performed by the SCF.

Without the above assumptions, the SC networks can still be analysed for arbitrary input signals and arbitrary switching patterns where both frequency domain and time domain information can be derived.[1] The analysis, however, is considerably more complex. For convenience or for practical reasons, most SC network designs are based on S/H input signal.

Thus this chapter only deals with the analysis of biphase SC network assuming sampled-and-held inputs. For this class of circuits, simple and fast analysis techniques are available but they only provide for the analytical evaluation of transfer functions and frequency responses of the SC circuits.

## 2.1 Analysis Techniques

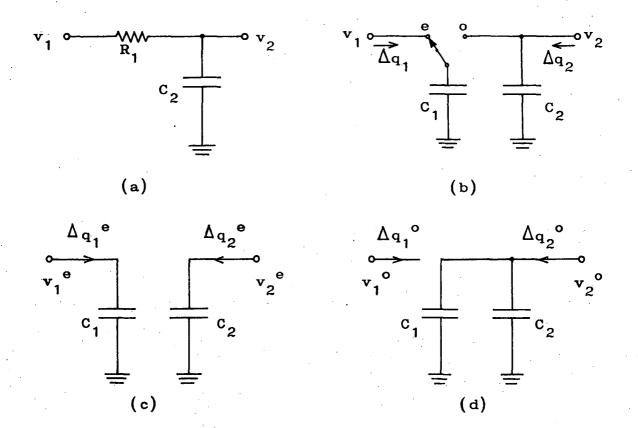

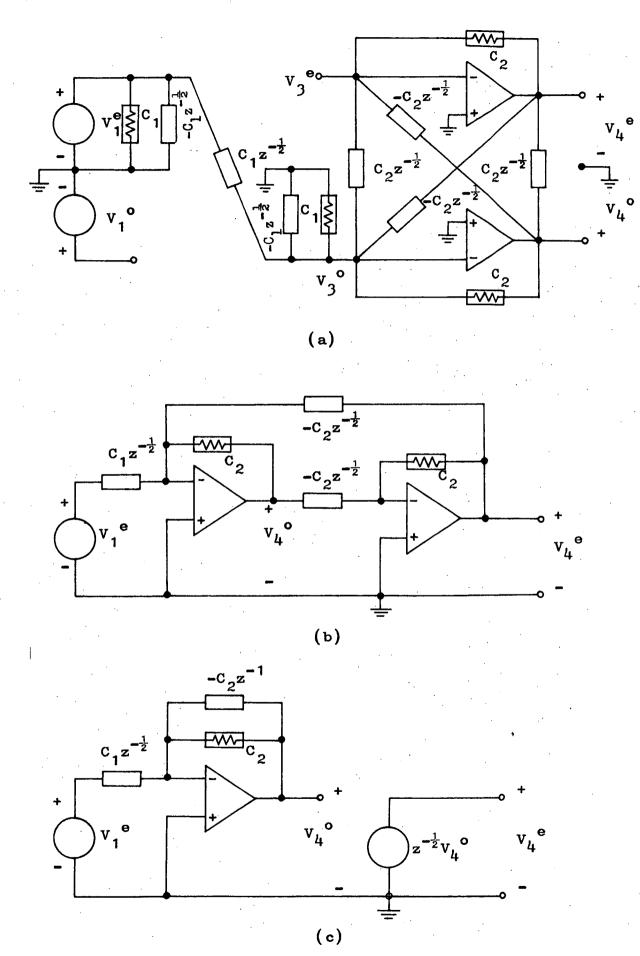

The use of the z-transform in the analysis of SC network is first illustrated here for the SC circuit in fig. 2:1(b) which corresponds to the simple RC circuit of fig. 2:1(a). The resistor of the RC circuit is replaced by the switched-capacitor of fig. 1:1. The SC circuit is assumed to comprise of ideal switches and capacitors. The switches are controlled by clock phases as shown in fig. 1:2(b).

The topology of the SC network is thus changed periodically between two states as shown in fig. 2:1(c) and (d). The port variables can be characterised in terms of discrete time voltages,  $v_{\rm x}({\rm k}\tau)$  and discrete time charge variation,  $\Delta q_{\rm x}({\rm k}\tau)$ , where x represents nodes in the circuit. At the switching time,  ${\rm k}\tau$ , when k is even, the SC network becomes that of fig. 2:1(c), and charges are instantaneously redistributed with the principle of charge conservation maintained at every node. Using this principle, nodal charge equations can be written at each node for the even sampling instants. These are

$$\Delta q_1^e(k\tau) = C_1 v_1^e(k\tau) - C_1 v_2^o[(k-1)\tau]$$

(2:1a)

$$\Delta q_2^e(k\tau) = C_2 v_2^e(k\tau) - C_2 v_2^o[(k-1)\tau]$$

(2:1b)

The superscripts e and o differentiate the variables of the two states.

At the switching time,  $k\tau$ , when k is odd, the network becomes that of fig. 2:1(d) and the nodal charge equations for this instant are

$$\Delta q_1^{o}(k\tau) = 0 \qquad (2:1c)$$

$$\Delta q_2^{o}(k\tau) = C_1 v_2^{o}(k\tau) + C_2 v_2^{o}(k\tau) - C_1 v_1^{e}[(k-1)\tau] - C_2 v_2^{e}[(k-1)\tau] \qquad (2:1d)$$

Applying the z-transform, where  $z = \exp(sT)$  in which s is the complex analogue frequency variable and  $T = 2\tau$ , eqns (2:1) becomes

$$\Delta Q_{1}^{e}(z) = C_{1}V_{1}^{e}(z) - z^{-\frac{1}{2}}C_{1}V_{2}^{o}(z) \qquad (2:2a)$$

$$\Delta Q_{2}^{e}(z) = C_{2}V_{2}^{e}(z) - z^{-\frac{1}{2}}C_{2}V_{2}^{o}(z) \qquad (2:2b)$$

$$\Delta Q_{1}^{o}(z) = 0 \qquad (2:2c)$$

$$\Delta Q_{2}^{o}(z) = C_{1}V_{2}^{o}(z) + C_{2}V_{2}^{o}(z) - z^{-\frac{1}{2}}C_{1}V_{1}^{e}(z) - z^{-\frac{1}{2}}C_{2}V_{2}^{e}(z) \qquad (2:2d)$$

where  $\Delta Q(z)$  and V(z) are z-transforms of  $\Delta q(k\tau)$  and  $V(k\tau)$  respectively.

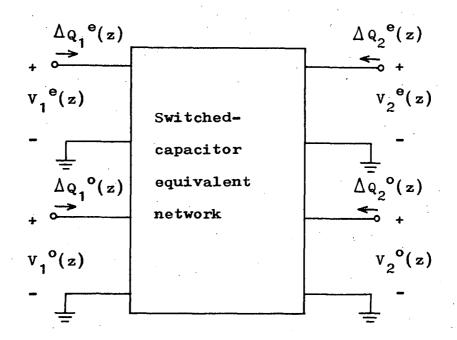

Thus at a particular node of the SC network of fig. 2:1(b), two distinct, but coupled, nodal charge equations are required to characterise the charge conservation. Eqn (2:2) can be written in matrix form as follows

$$\begin{bmatrix} \Delta Q_{1}^{e} \\ \Delta Q_{2}^{e} \\ \Delta Q_{1}^{o} \\ \Delta Q_{2}^{o} \end{bmatrix} = \begin{bmatrix} c_{1} & 0 & 0 & -z^{-\frac{1}{2}}C_{1} \\ 0 & c_{2} & 0 & -z^{-\frac{1}{2}}C_{2} \\ 0 & 0 & 0 & 0 \\ -z^{-\frac{1}{2}}C_{1} & -z^{-\frac{1}{2}}C_{2} & 0 & c_{1}+c_{2} \end{bmatrix} \begin{bmatrix} v_{1}^{e} \\ v_{2}^{e} \\ v_{1}^{o} \\ v_{2}^{o} \end{bmatrix}$$

(2:3)

The transfer functions describing the circuit can be obtained from (2:3) using cofactor techniques. Let [Y] represent the matrix, these transfer functions are

Fig. 2:1 (a) RC circuit. (b) A switched-capacitor network simulating the RC circuit. (c) network (b) during the even clock phase. (d) network (b) during the odd clock phase.

Fig.2:2 Four-port equivalent of a two-port switched capacitor network.

$$H^{ee} = \frac{v_2^e}{v_1^e} = \frac{|Y_{12}|}{|Y_{11}|} = \frac{c_1 z^{-1}}{c_1 + c_2 - c_2 z^{-1}}$$

(2:4a)

$$H^{eo} = \frac{v_2^o}{v_1^e} = \frac{|Y_{14}|}{|Y_{11}|} = \frac{c_1^{z^{-\frac{1}{2}}}}{c_1 + c_2 - c_2^{z^{-1}}}$$

(2:4b)

$$H^{0e} = \frac{v_{2}^{e}}{v_{1}^{o}} = \frac{|Y_{32}|}{|Y_{33}|} = 0$$

(2:4c)

$$H^{00} = \frac{V_2^0}{V_1^0} = \frac{|Y_{34}|}{|Y_{33}|} = 0$$

(2:4d)

The SC network is thus fully characterised by the input-output relation,

$$\begin{bmatrix} v_2^e(z) \\ v_2^o(z) \end{bmatrix} = \begin{bmatrix} H^{ee} & H^{oe} \\ H^{eo} & H^{oo} \end{bmatrix} \begin{bmatrix} v_1^e(z) \\ v_1^o(z) \end{bmatrix}$$

(2:5a)

where

$$V_1(z) = V_1^e(z) + V_1^o(z)$$

(2:5b)

$$V_2(z) = V_2^e(z) + V_2^o(z)$$

(2:5c)

The SC network can then also be represented by an equivalent four-port as shown in fig. 2:2 where the equivalent z-domain network is described by (2:5a) or (2:3).

Signal conditioning performed at the input and output determines the relevant transfer function relations of the SC network. As an example, if the output is sampled only at the even  $k\tau$  time instants, then the relevant relation is

$$V_2^e(z) = H^{ee}V_1^e(z) + H^{oe}V_1^o(z)$$

(2:6)

In the circuit of fig. 2:1(b), however, the input at the odd  $k\tau$  time instants is not sampled, thus for this case only the transfer function  $H^{ee}$  is involved.

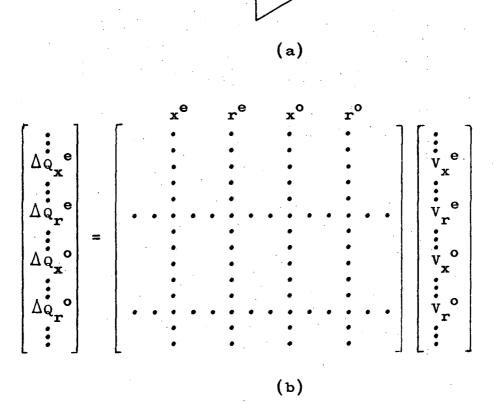

If a general SC network is now considered, the two z-transformed nodal charge equations at a particular node x are written as

$$\Delta Q_{\mathbf{x}}^{\mathbf{e}}(z) = \sum_{\mathbf{j}=1}^{\mathbf{Nex}} Q_{\mathbf{x}\mathbf{j}}^{\mathbf{e}}(z) - z^{-\frac{1}{2}} \sum_{\mathbf{j}=1}^{\mathbf{Nex}} Q_{\mathbf{x}\mathbf{j}}^{\mathbf{o}}(z)$$

(2:7a)

$$\Delta Q_{\mathbf{x}}^{\mathbf{o}}(\mathbf{z}) = \sum_{\mathbf{j}=1}^{\mathbf{Nox}} Q_{\mathbf{xj}}^{\mathbf{o}}(\mathbf{z}) - \mathbf{z}^{-\frac{1}{2}} \sum_{\mathbf{j}=1}^{\mathbf{Nox}} Q_{\mathbf{xj}}^{\mathbf{e}}(\mathbf{z})$$

(2:7b)

where Nex, Nox denote the total number of capacitors connected to node x during the even and odd clock phases respectively.  $Q_{xj}^e(z)$ ,  $Q_{xj}^o(z)$  are z-transforms of the instantaneous charges stored on the j-th capacitor connected to node x at the even and odd  $k\tau$  time instants respectively.

As the circuit increases in complexity, it becomes very difficult to write down (2:7). The transfer functions as in (2:5a) can no longer be easily obtained as for the case of the simple circuit of fig. 2:1(b). A number of analysis techniques have been proposed which simplify these steps. The following sections deal with two basic methods which are capable of handling any two-phase SC network containing ideal elements with S/H inputs. These are the nodal analysis technique [2] and the equivalent circuit method.[8] Based on these, more general methods have been developed but the following sections only elaborate them in their simplest forms.

## 2.2 Nodal Analysis Technique

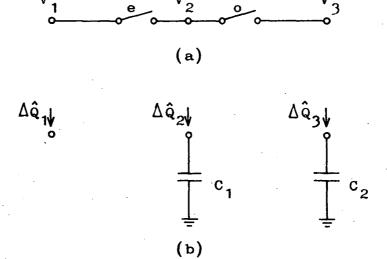

Using (2:7), the total number of equations involved to describe a SC network is 2n, where n is the number of nodes in the network. In this nodal analysis technique, the network is broken down into switches and capacitors networks. Using matrices which describe these networks, equations such as in (2:7) can be assembled in a logical manner. This method is particularly attractive for computer analysis of SC networks.

In this analysis, it is first assumed that any branch between two nodes in the network consists only of a capacitor and a switch. Thus another node has to be introduced for the circuit of fig. 2:1(b) for its analysis using this method. The circuit is redrawn in fig. 2:3 broken down into its switches and capacitors networks with the nodes renumbered. In this way, the same capacitors are connected to each node at all time instants. Thus, from fig. 2:3(b), a fixed capacitance matrix can be written as follows,

$$[C] = \begin{bmatrix} 0 & 0 & 0 \\ 0 & C_1 & 0 \\ 0 & 0 & C_2 \end{bmatrix}$$

(2:8)

The voltage at each node is determined by the switch connection. Thus when switch e closes, taking  ${\rm V_1}^{\rm e}$  as the reference in fig. 2:3(a),

$$v_1^e = v_1^e$$

,  $v_2^e = v_1^e$ ,  $v_3^e = v_3^e$  (2:9)

These can be written in matrix form as

$$\begin{bmatrix} v_1^e \\ v_2^e \\ v_3^e \end{bmatrix} = \begin{bmatrix} 1 & 0 & 0 \\ 1 & 0 & 0 \\ 0 & 0 & 1 \end{bmatrix} \begin{bmatrix} v_1^e \\ v_2^e \\ v_3^e \end{bmatrix} = [S^e]v^e \quad (2:10)$$

where  $[S^e]$  is the even switching matrix and  $V^e$  is the corresponding vector of the voltages at the nodes of the circuit. Similarly, when switch o closes, the switching matrix  $[S^o]$  can be obtained and the corresponding vector  $V^o$  defined as

$$\begin{bmatrix} S^{\circ} \end{bmatrix} = \begin{bmatrix} 1 & 0 & 0 \\ 0 & 0 & 1 \\ 0 & 0 & 1 \end{bmatrix}, \quad V^{\circ} = \begin{bmatrix} v_{1}^{\circ} \\ v_{2}^{\circ} \\ v_{3}^{\circ} \end{bmatrix}$$

(2:11)

Equations such as in (2:7) can then be written in matrix form as follows

$$\begin{bmatrix} \Delta \hat{Q}^{e} \\ \Delta \hat{Q}^{o} \end{bmatrix} = \begin{bmatrix} [C] & [0] \\ [0] & [C] \end{bmatrix} \begin{bmatrix} [S^{e}] & -z^{-\frac{1}{2}}[S^{o}] \\ -z^{-\frac{1}{2}}[S^{e}] & [S^{o}] \end{bmatrix} \begin{bmatrix} v^{e} \\ v^{o} \end{bmatrix}$$

(2:12)

where, due to the different node definition,  $\Delta Q(z)$  is now used to denote the z-transformed charge variation.  $\Delta \hat{Q}^e$  and  $\Delta \hat{Q}^o$  are vectors of the z-transformed charge variations at nodes of the network when switches e and o close, respectively.

The closing of the switches reduces the actual number of nodes in the circuit. This has to be taken into account by using the charge matrices [I<sup>e</sup>] and [I<sup>o</sup>] for the even and odd kt time instants respectively. When switch e closes in fig. 2:3, the actual charge variation at the combined node is the combination of  $\Delta \hat{Q}_1$  and  $\Delta \hat{Q}_2$  which have been assumed to be present on nodes 1 and 2 separately. Thus taking node 1 as reference, the combined charge variations are

Fig. 2:3 (a) Switches network of the circuit in fig. 2:1(b).

(b) Its capacitors network.

Fig. 2:4 (a) An ideal voltage amplifier between nodes x and r in a switched-capacitor network. (b) The matrix [Y] showing the affected rows and columns with the inclusion of the amplifier.

$$\Delta Q_1^e = \Delta \hat{Q}_1^e + \Delta \hat{Q}_2^e, \ \Delta Q_2^e = 0$$

(2:13a)

and since switch o is open at this instant,

$$\Delta Q_3^e = \Delta \hat{Q}_3^e \tag{2:13b}$$

These are written in matrix form as

$$\Delta Q^{e} = \begin{bmatrix} \Delta Q_{1}^{e} \\ \Delta Q_{2}^{e} \\ \Delta Q_{3}^{e} \end{bmatrix} = \begin{bmatrix} 1 & 1 & 0 \\ 0 & 0 & 0 \\ 0 & 0 & 1 \end{bmatrix} \begin{bmatrix} \hat{\Delta Q_{1}^{e}} \\ \hat{\Delta Q_{2}^{e}} \\ \hat{\Delta Q_{3}^{e}} \end{bmatrix} = [I^{e}] \hat{\Delta Q^{e}} (2:14)$$

Similarly when switch o closes, the matrix equation is

$$\Delta Q^{O} = \begin{bmatrix} \Delta Q_{1}^{O} \\ \Delta Q_{2}^{O} \\ \Delta Q_{3}^{O} \end{bmatrix} = \begin{bmatrix} 1 & 0 & 0 \\ 0 & 0 & 0 \\ 0 & 1 & 1 \end{bmatrix} \begin{bmatrix} \Delta \hat{Q}_{1}^{O} \\ \Delta \hat{Q}_{2}^{O} \\ \Delta \hat{Q}_{3}^{O} \end{bmatrix} = [I^{O}] \Delta \hat{Q}^{O} \quad (2:15)$$

Hence, in general, all the nodal charge equations can be assembled in matrix form as follows [2], using (2:12), (2:14) and (2:15);

$$\begin{bmatrix} \Delta Q^{e} \\ \Delta Q^{o} \end{bmatrix} = \begin{bmatrix} [I^{e}][C][S^{e}] & -z^{-\frac{1}{2}}[I^{e}][C][S^{o}] \\ -z^{-\frac{1}{2}}[I^{o}][C][S^{e}] & [I^{o}][C][S^{o}] \end{bmatrix} \begin{bmatrix} v^{e} \\ v^{o} \end{bmatrix}$$

(2:16)

or

$$\Delta Q = [Y]V$$

For the circuit of fig. 2:1(b), the same matrix equation as in (2:3) is obtained after elimination of rows and columns of the matrix [Y] which are zero, and their corresponding variables.

The switches and capacitors have been assumed ideal. The presence of parasitic capacitance can, however, be easily incorporated in the analysis. The analysis can also accommodate the presence of an ideal voltage amplifier with gain,  $-A_O$  as shown in fig. 2:4(a) connected between

nodes x and r. The voltages at the nodes are related by  $v_x^e = -\frac{v_r^e}{A_0}$ ,  $v_x^o = -\frac{v_r^o}{A_0}$  (2:17)

The matrix [Y] is shown in fig. 2:4(b) showing only variables, rows and columns of the relevant nodes. Using (2:17), column  $\mathbf{x}^{\mathbf{e}}$  of the matrix is divided by  $\mathbf{A}_{\mathbf{0}}$  and subtracted from column  $\mathbf{r}^{\mathbf{e}}$  and column  $\mathbf{x}^{\mathbf{e}}$  is discarded. Similar steps are done for columns  $\mathbf{x}^{\mathbf{0}}$  and  $\mathbf{r}^{\mathbf{0}}$ . The rows involving  $\Delta Q_{\mathbf{r}}^{\mathbf{e}}$  and  $\Delta Q_{\mathbf{r}}^{\mathbf{0}}$  are also discarded since they express the current outputs from a voltage source and thus are redundant. When  $\mathbf{A}_{\mathbf{0}}^{\mathbf{+}}$  on for an ideal OA, these steps merely involve discarding columns  $\mathbf{x}^{\mathbf{e}}$ ,  $\mathbf{x}^{\mathbf{0}}$  and rows involving  $\Delta Q_{\mathbf{r}}^{\mathbf{e}}$ ,  $\Delta Q_{\mathbf{r}}^{\mathbf{0}}$ .[3]

Thus normally the matrix [Y] can be reduced to at most a 4 x 4 matrix as in (2:3). If necessary, pivotal condensation can be applied to reduce the matrix. Then, after considering the signal conditioning to the SC network, cofactor techniques are used as before to derive the relevant transfer functions of the network.

This technique can be extended for the analysis of multiphase SC networks [4] and SC network using amplifier with finite gain and finite bandwidth.[5] Computer programs for the analysis of SC networks based on this technique have been implemented. However, most computer-aided-design (CAD) programs use the more efficient modified nodal analysis (MNA) techniques for the computation of SC network.[6][7]

#### 2.3 Equivalent Circuit Method

This method involves deriving simple z-domain equivalent circuits or building blocks for several elements of the SC network using the

z-transformed nodal charge equations as in (2:7). Any SC network can then be transformed into a z-domain equivalent circuit by interconnecting the appropriate building blocks. It is then possible to apply familiar network analysis techniques on the SC network equivalent circuit to derive the transfer relations between any pair of nodes of the network. This method is appealing from the practical insight view.

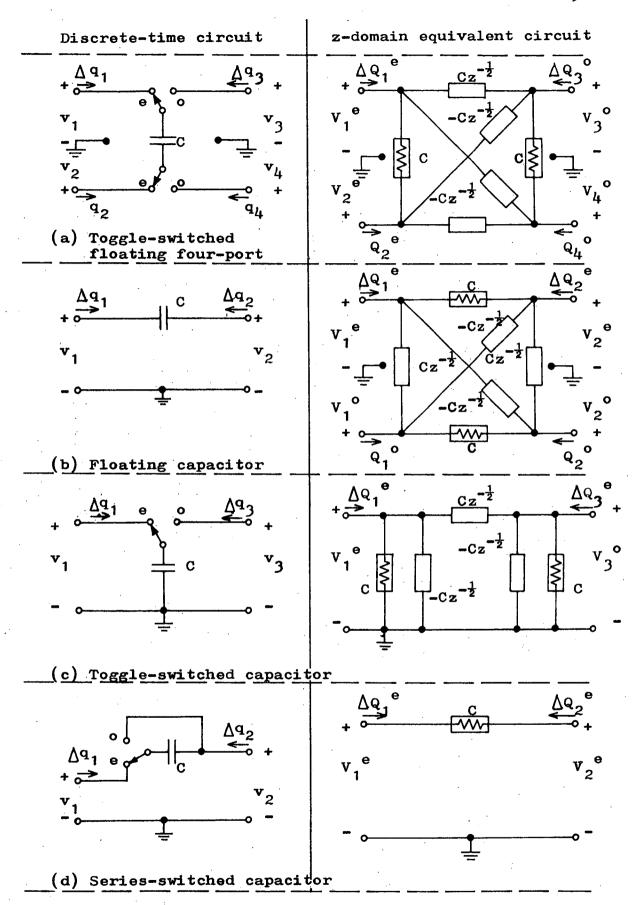

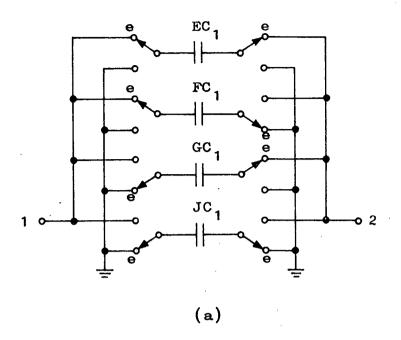

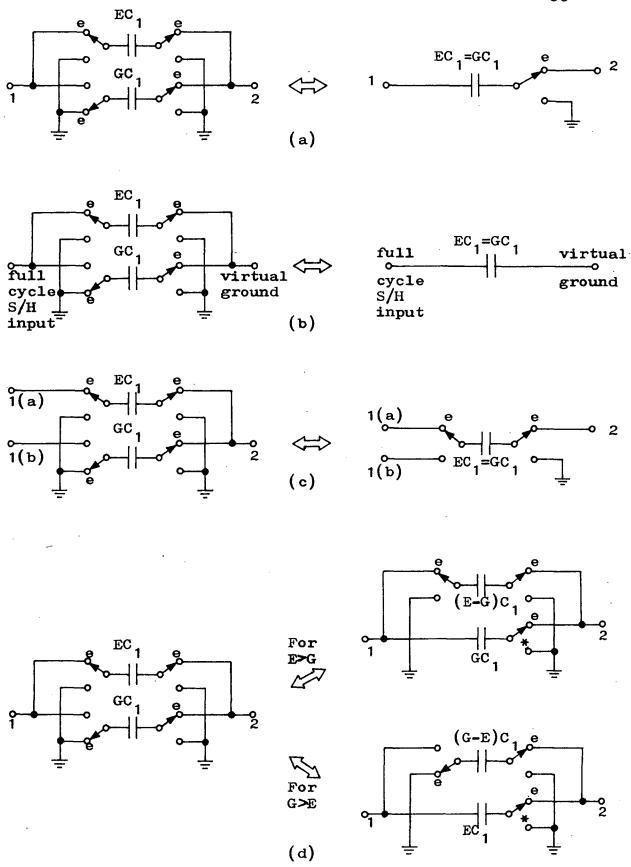

The circuit shown in fig. 2:5 is the most general switched (single) capacitor element. Other SC elements are specific cases of its configuration. Thus only its equivalent circuit needs to be derived directly from the z-transformed nodal charge equations. By manipulating this equivalent circuit, the other useful SC building blocks can then be derived. These blocks, together with the equivalent circuits for independent and voltage-controlled voltage sources form a library of building blocks which can be used for both the analysis and synthesis of biphase SC networks.[8][9] This method of analysis has also been extended so that it can be applicable for multiphase SC network [10] and biphase SC network with continuous input signals, and duty cycle not equal to 50%.[11]

The z-transformed nodal charge equations for the toggle-switched floating four-port (TSFFP) in fig. 2:5 can be written as follows

$$\Delta Q_{1}^{e}(z) = CV_{1}^{e}(z) - CV_{2}^{e}(z) - Cz^{-\frac{1}{2}}V_{3}^{o} + Cz^{-\frac{1}{2}}V_{4}^{o} \quad (2:18a)$$

$$\Delta Q_{1}^{o}(z) = 0 \quad (2:18b)$$

$$\Delta Q_{2}^{e}(z) = CV_{2}^{e}(z) - CV_{1}^{e}(z) - Cz^{-\frac{1}{2}}V_{4}^{o} + Cz^{-\frac{1}{2}}V_{3}^{o} \quad (2:18c)$$

$$\Delta Q_{2}^{o}(z) = 0 \quad (2:18d)$$

$$\Delta Q_{3}^{e}(z) = 0 \quad (2:18e)$$

$$\Delta Q_{3}^{o}(z) = CV_{3}^{o}(z) - CV_{4}^{o}(z) - Cz^{-\frac{1}{2}}V_{1}^{e} + Cz^{-\frac{1}{2}}V_{2}^{e} \quad (2:18f)$$

$$\Delta Q_{4}^{e}(z) = 0 \quad (2:18g)$$

$$\Delta Q_{4}^{o}(z) = CV_{4}^{o}(z) - CV_{3}^{o}(z) - Cz^{-\frac{1}{2}}V_{2}^{e} + Cz^{-\frac{1}{2}}V_{1}^{e} \quad (2:18h)$$

Fig. 2:5 Toggle-switched floating four-port. [8]

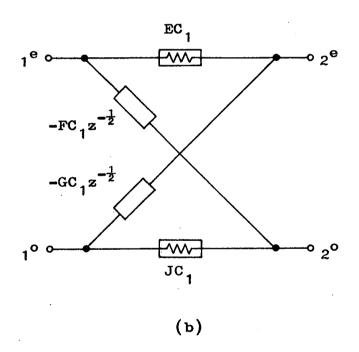

Equation (2:18) describes an eight-port equivalent circuit with four open ports. These open ports can be deleted and the remaining equations in (2:18) are used to derive the four-port equivalent circuit shown in fig. 2:6(a) for the TSFFP. Note that the even (e) and odd (o) phases are interchangeable on the SC circuit, i.e. if the capacitor in fig. 2:5 is connected to  $V_1$  and  $V_2$  during the o phase and to  $V_3$  and  $V_4$  during the e phase, then the equivalent circuit is obtained by interchanging the superscripts of the variables of the equivalent circuit in fig. 2:6(a).

The TSFFP is equivalent to the floating capacitor in fig. 2:6(b) if  $V_3 = V_1$  and  $V_4 = V_2$ . Thus the equivalent circuit for the floating capacitor can be derived from that of the TSFFP by making similar replacement of the subscripts for its variables. The toggle-switched capacitor of fig. 2:6(c) can be obtained by grounding  $V_2$  and  $V_4$  of the TSFFP. Thus the corresponding equivalent circuit is similarly obtained. The series-switched capacitor of fig. 2:6(d) is obtained by shorting  $V_3$  and  $V_4$  of the TSFFP and its equivalent circuit is as shown. Other SC z-domain equivalent circuits can similarly be derived.

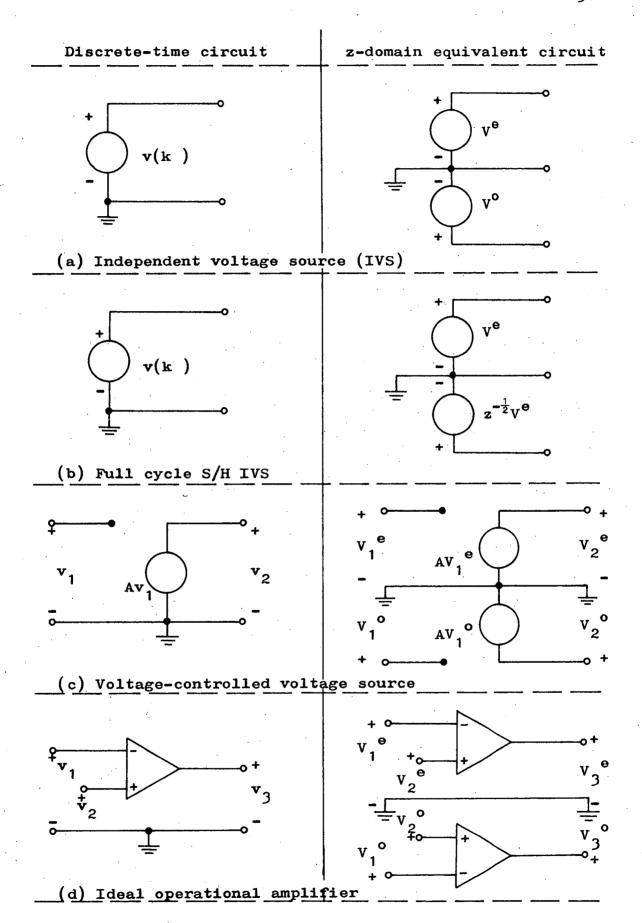

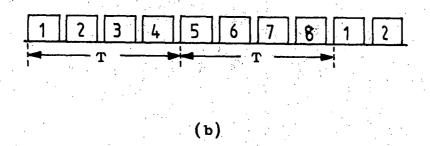

The independent voltage source and its corresponding equivalent circuit is shown in fig. 2:7(a), where the voltage source is split into two for the even and odd phases. The equivalent circuit for the full cycle sampled-and-held independent voltage source, the voltage controlled voltage source and the ideal OA are shown in fig. 2:7(b), (c) and (d) respectively. Thus fig. 2:6 and fig. 2:7 give a sample of equivalent circuits which are often used, from the library of z-domain equivalent circuits for switched-capacitor building blocks.[8] From these equivalent circuits, the SC network of fig. 2:1(b), for example, can be analysed

Fig. 2:6 z-domain equivalent circuits for switchedcapacitor elements

Fig. 2:7 z-domain equivalent circuits for voltage sources.

by appropriately interconnecting the blocks in fig. 2:6(b) and (c), and the source in fig. 2:7(a).

## 2.4 Examples

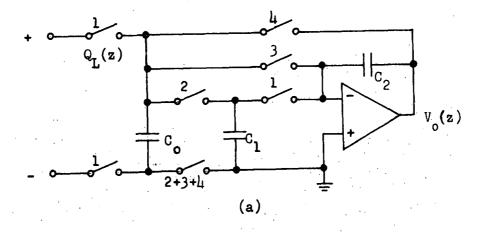

The SC network shown in fig. 2:8 will be used to further demonstrate the two methods of analyses described. The network is actually a circuit for the switched-capacitor integrator (SCI) as will be shown in chapter 3. The relevant transfer functions as defined in (2:5) for this circuit are derived.

Deriving transfer functions using nodal analysis technique.

The circuit in fig. 2:8 has its nodes numbered as shown. The

switches and capacitors networks of the circuit can then be drawn

separately as in fig. 2:9. From fig. 2:9(a), the following matrices can be written

(2:19)

$$\begin{bmatrix} \mathbf{I}^{\mathbf{e}} \end{bmatrix} = \begin{bmatrix} 1 & 1 & 0 & 0 \\ 0 & 0 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 \end{bmatrix} \qquad \begin{bmatrix} \mathbf{I}^{\mathbf{o}} \end{bmatrix} = \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 \\ 0 & 1 & 1 & 0 \\ 0 & 0 & 0 & 1 \end{bmatrix}$$

From fig. 2:9(b), the capacitor matrix is

$$\begin{bmatrix} \mathbf{C} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & 0 \\ 0 & \mathbf{C}_1 & 0 & 0 \\ 0 & 0 & \mathbf{C}_2 & -\mathbf{C}_2 \\ 0 & 0 & -\mathbf{C}_2 & \mathbf{C}_2 \end{bmatrix}$$

(2:20)

Fig. 2:8 A switched-capacitor integrator.

Fig. 2:9 (a) Switches network of the switched-capacitor integrator. (b) Capacitors network of the switched-capacitor integrator.

Putting (2:19) and (2:20) in (2:16), the following matrix equation is obtained,

The zero columns and rows of the matrix in (2:21) can be eliminated. Also, the presence of the ideal OA between nodes 3 and 4 makes it possible to discard columns 3 (even), 3 (odd) and rows 4 (even), 4 (odd). Thus the reduced matrix equation is

$$\begin{bmatrix} \Delta Q_{1}^{e} \\ \Delta Q_{3}^{e} \\ \Delta Q_{3}^{o} \end{bmatrix} = \begin{bmatrix} c_{1} & 0 & 0 \\ 0 & -c_{2} & z^{-\frac{1}{2}} c_{2} \\ -z^{-\frac{1}{2}} c_{1} & z^{-\frac{1}{2}} c_{2} & -c_{2} \end{bmatrix} \begin{bmatrix} v_{1}^{e} \\ v_{4}^{e} \\ v_{4}^{o} \end{bmatrix}$$

(2:22)

Note that  $V_1^{\circ}$  is absent in (2:22) since the input is only sampled during the even clock phase. The relevant transfer functions of the SCI are

$$H^{ee} = \frac{v_4^e}{v_1^e} = \frac{|Y_{12}|}{|Y_{11}|} = \frac{-c_1 z^{-1}}{c_2 (1 - z^{-1})}$$

(2:23a)

$$H^{eo} = \frac{v_4^o}{v_1^e} = \left| \frac{v_{13}}{v_{11}} \right| = \frac{-c_1 z^{-\frac{1}{2}}}{c_2 (1 - z^{-1})}$$

(2:23b)

2. Deriving transfer functions using equivalent circuit method.

By properly interconnecting the SC building blocks of fig. 2:6(b), (c) and fig. 2:7(a),(d), the SCI in fig. 2:8 is transformed into its z-domain equivalent circuit shown in fig. 2:10(a). This can be simplified by removing elements shunting virtual ground points and voltage sources. The simplified circuit is shown in fig. 2:10(b) which can be reconfigured into the circuit in fig. 2:10(c).[8] The relevant transfer functions can then be easily obtained to be

$$H^{ee} = \frac{v_4^e}{v_1^e} = -\frac{c_1 z^{-1}}{c_2 (1 - z^{-1})}$$

(2:24a)

$$H^{eo} = \frac{v_4^o}{v_1^e} = -\frac{c_1 z^{-\frac{1}{2}}}{c_2 (1 - z^{-1})}$$

(2:24b)

which are the same as in (2:23). Note that  $H^{ee} = z^{-\frac{1}{2}}H^{eo}$ , i.e. the output of the SCI is held over the full clock cycle.

## 3. Frequency responses

The above z-transform techniques accurately predict the input-output relationship of the SCI on a sample-by-sample basis. The frequency response on this basis is obtained by setting  $z = \exp(j\omega T)$ . However, in between these samples, the output of the SCI has the held, staircase-like wave shape. This analogue character of the circuit can be taken into account by multiplying the z-transform-computed frequency response with  $(\sin \omega T/2)/(\omega T/2)$ . For high sampling rates, where  $\omega T <<1$ , the passband of the frequency response is virtually unaffected.

Fig. 2:10 Equivalent circuits of the switched-capacitor integrator in fig. 2:8.

#### REFERENCES

- [1] Y.P. Tsividis, "Analysis of Switched Capacitive Networks", IEEE Trans. Circuits Syst., 1979, Vol. CAS-26, pp.935-946.

- [2] C.F. Kurth, G.S. Moschytz, "Nodal Analysis of Switched-Capacitor Networks", *IEEE Trans. Circuits Syst.*, 1979, Vol. CAS-26, pp.93-104.

- [3] J.I. Sewell, "Analysis of Active Switched-Capacitor Networks", Proc. IEEE, 1980, Vol. 68, pp.292-293.

- [4] E. Hokenek, G.S. Moschytz, "Analysis of multiphase switched-capacitor (m.s.c.) Networks using the indefinite admittance matrix (i.a.m.)", IEE Proc., 1980, Vol. 127, Pt.G, pp.226-241.

- [5] J. Lau, J.I. Sewell, "Inclusion of Amplifier Finite Gain and Bandwidth in Analysis of Switched-Capacitor Filters", *Electron*. *Lett.*, 1980, Vol. 16, pp.462-463.

- [6] J. Vondewalle, H.J. DeMan, J. Rabaey, "Time, Frequency, and z-Domain Modified Nodal Analysis of Switched-Capacitor Networks", *IEEE Trans. Circuits Syst.*, 1981, Vol. CAS-28, pp.186-195.

- [7] R. Plodeck, U.W. Brugger, D.C. von Grunigen, G.S. Moschytz, "SCANAL A program for the computer-aided analysis of switched-capacitor networks", *IEE Proc.*, 1981, Vol. 128, Pt. G, pp.277-285.

- [8] K.R. Laker, "Equivalent Circuits for the Analysis and Synthesis of Switched Capacitor Networks", Bell Syst. Tech. J., 1979, Vol. 58, pp.729-769.

- [9] F. Anday, "Realization of second-order transfer functions with switched-capacitor networks", *Int. J. Electronics*, 1981, Vol. 50, pp.169-174.

- [10] J.J. Mulawka, "By-inspection analysis of switched-capacitor networks", *ibid.*, 1980, Vol. 49, pp.359-373.

- [11] C.F. Kurth, "Two-Port Analysis of SC Networks with Continuous Input Signals", Bell Syst. Tech. J., 1980, Vol. 59, pp.1297-1316.

#### CHAPTER THREE

## SWITCHED-CAPACITOR INTEGRATORS

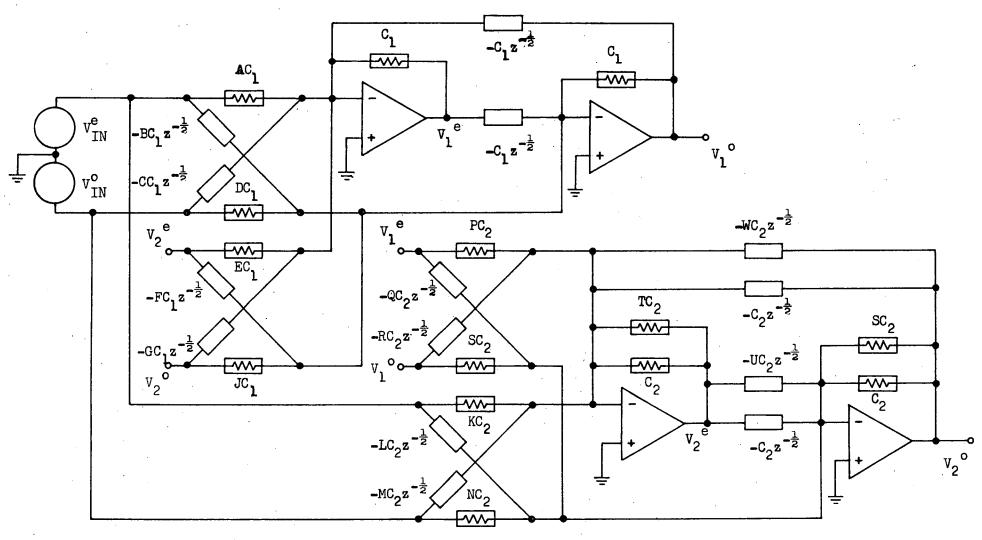

An attractive technique for the design of switched-capacitor filters is based on active-RC filters which use integrators as building blocks. These include state-variable biquadratic circuits which are used in cascade design and leap-frog filters which simulate the operation of low-sensitivity, doubly-terminated LC ladder networks. The integrators in active-RC filters can simply be replaced by active switched-capacitor integrators (SCIs) such as given in fig. 2:8. The presence of the operational amplifier in each integrator makes it possible to eliminate effects of parasitics, thus ensuring accurate and reproducible filters. These features make the technique a popular approach for SCF design. Thus the SCIs form an important part of many realisable SCFs.

Hence, its development is discussed in detail in the following sections.

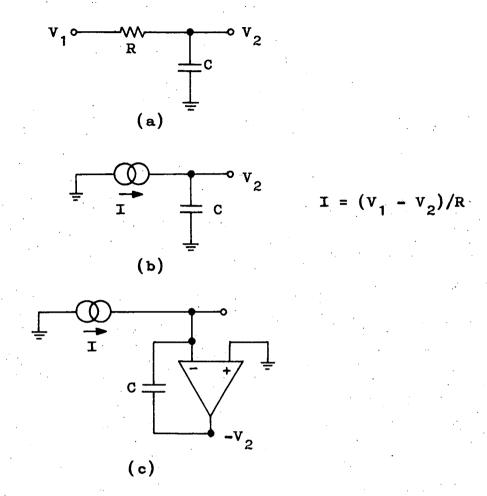

## 3.1 Transfer Functions

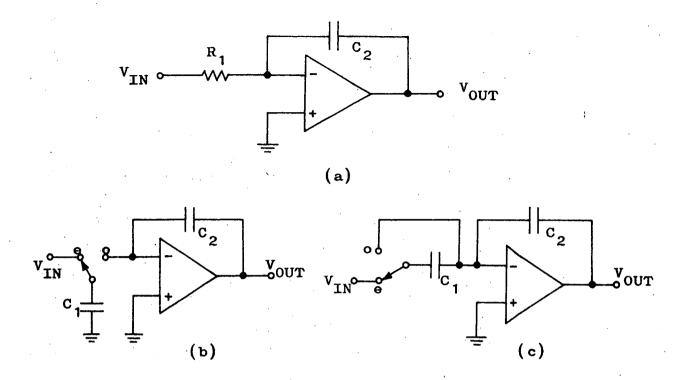

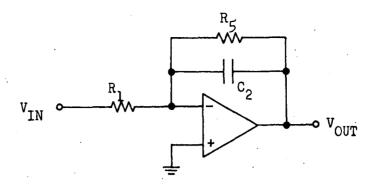

Fig. 3:1(a) shows the conventional analogue integrator with transfer function

$$H(s) = -\frac{1}{R_1 C_2 s}$$

(3:1)

Originally, the SCI is developed from the analogue integrator by replacing the resistor with its switched-capacitor equivalent discussed in chapter 1.[1][2] Using the switched-capacitor "resistor" of fig. 1:1, results in the SCI in fig. 3:1(b) as in fig. 2:8, which has been referred to as the toggle-switched integrator. With  $R_1 = 1/(f_c C_1)$ , assuming frequencies much less than the clock rate,  $f_c$ , the frequency response of the SCI is given by, (setting  $s = j\omega$ )

$$H(\omega) = - \operatorname{fc} \left[ \frac{C_1}{C_2} \right] \frac{1}{j\omega}$$

(3:2)

Using the series switched capacitor in fig. 1:3, the integrator in fig. 3:1(c) is obtained.

Eqn. (3:2) shows that the integrator gain is dependent on a capacitor ratio and the clock frequency. The ability to obtain precise capacitor ratios and a very stable clock means that precision integrator gain can be produced.

However, the actual frequency response of the SCI deviates from that of the analogue integrator, especially for frequencies approaching the clock frequency. Due to its sampled-data nature, a more exact analysis using z-transform techniques as discussed in chapter 2 has to be used. The transfer function of the SCI when the output is sampled during the even interval is (see eqn. (2:24a))

$$H^{ee} = -\frac{C_1}{C_2} \cdot \frac{z^{-1}}{1-z^{-1}}$$

(3:3)

By setting  $z = \exp(j\omega T)$  where  $T = 1/f_c$ , the frequency response is then given by

$$H(\omega) = -f_{c} \frac{c_{1}}{c_{2}} \cdot \frac{1}{j_{\omega}} \left[ \frac{\omega T}{2\sin(\frac{\omega T}{2})} \right] \exp(-\frac{j_{\omega}T}{2}) \quad (3:4)$$

Comparing (3:2) and (3:4), both magnitude and phase deviations are present in the frequency response of the SCI, especially when  $\omega$ T<<1 is not satisfied. The magnitude deviation is not significant. However, the excess phase shift is important in that it will cause distortion in the form of Q-enhancement in which the response of the complete filter shows some undesired peaking. [3]

If eqns (3:1) and 3:3) are compared, then it can be seen that

Fig. 3:1 (a) Analogue integrator. (b) Toggle-switched integrator. (c) Series-switched integrator.

Fig. 3:2 A two-integrator loop with proper switch phasing.

implementing the integrator as in fig. 3:1(b) realise the mapping

$$s \to \frac{1}{T} = \frac{1 - z^{-1}}{z^{-1}}$$

(3:5)

which is the forward difference transformation. This transforms the imaginary axis in the s-plane to the vertical line going through z=1 in the z-plane instead of onto the unit circle. Thus it maps high-Q s-plane poles and zeros into z-plane poles and zeros which are very close to the unit circle or even outside it.

For the integrator in fig. 3:1(c), its transfer functions can be obtained from its equivalent circuit in which blocks of fig. 2:6(b), (d) and fig. 2:7(a), (d) are interconnected. When its output is sampled during the even interval, the transfer function is,

$$H^{ee} = -\frac{C_1}{C_2} \frac{1}{1-z} - 1 \tag{3:6}$$

Comparing (3:1) and (3:6), this implements the backward difference transformation.

$$s \rightarrow \frac{1}{T} (1 - z^{-1})$$

(3:7)

This maps the imaginary axis of the s-plane inside the unit circle of the z-plane.

The excess phase shift in (3:4) can be eliminated if the output is sampled during the odd interval.[4] Hence, as in eqn. (2:24b), the transfer function of the SCI is

$$H^{\text{eo}} = -\frac{C_1}{C_2} \frac{z^{-\frac{1}{2}}}{1 - z^{-1}}$$

(3:8)

which gives the frequency response,

$$H(\omega) = -\frac{f_c^C_1}{C_2} \cdot \frac{1}{j\omega} \left[ \frac{\omega T}{2\sin(\omega T/2)} \right]$$

(3:9)

Thus, if the switch phasing in the overall circuit of the filter ensures that the output of the integrator is sampled correctly, then the undesirable effects due to the excess phase shift can be avoided. This implementation is equivalent to realising the lossless discrete integrator (LDI) transformation

$$s \to \frac{1}{T} = \frac{1 - z^{-1}}{z^{-\frac{1}{2}}}$$

(3:10)

The LDI transformation, maps the imaginary axis of the s-plane onto the unit circle of the z-plane and ensure stable s-domain transfer functions map into stable z-domain transfer functions. The magnitude deviation as in (3:9) is due to the fact that only the portion  $-\frac{2}{T} < \Omega < \frac{2}{T}$  of the imaginary axis of the s-plane is mapped onto the unit circle. The deviation can thus be adjusted, if necessary, by prewarping the continuous-time filter frequency,  $\Omega$  using

$$\Omega = \frac{2}{T} \sin \left(\frac{\omega T}{2}\right) \tag{3:11}$$

i.e. by replacing  $\omega$  in (3:2) by  $\Omega$ , (3:2) becomes equivalent to (3:9).

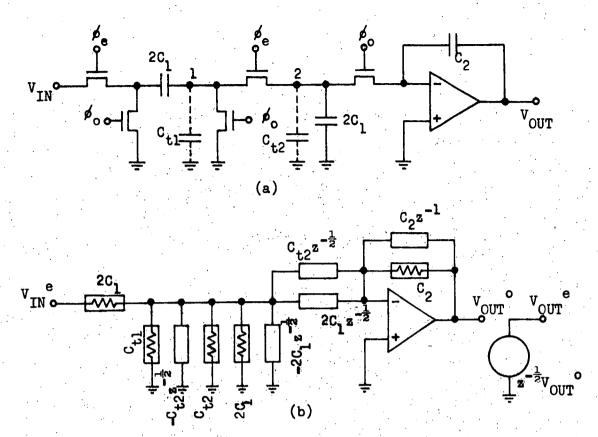

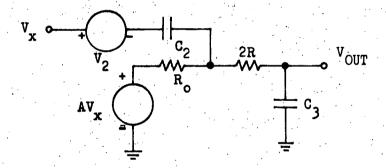

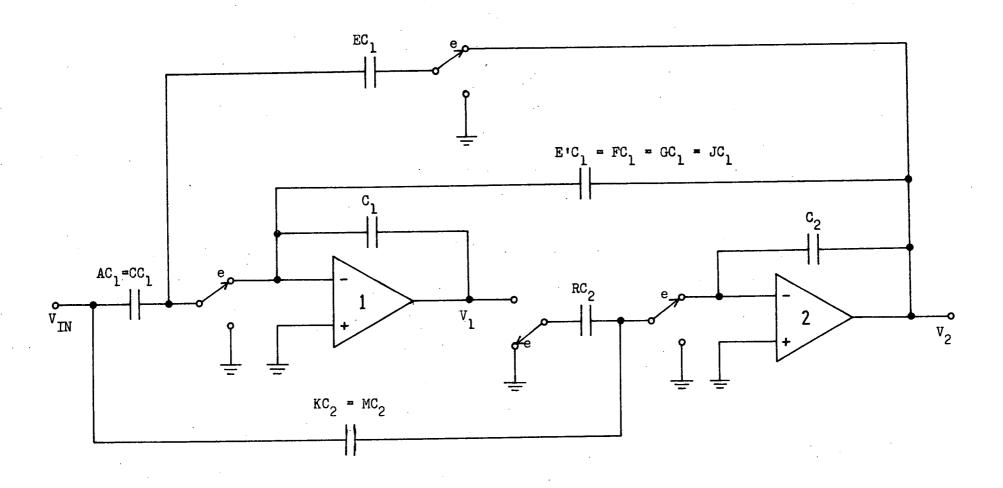

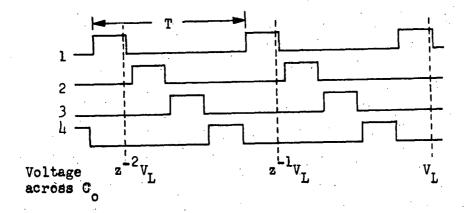

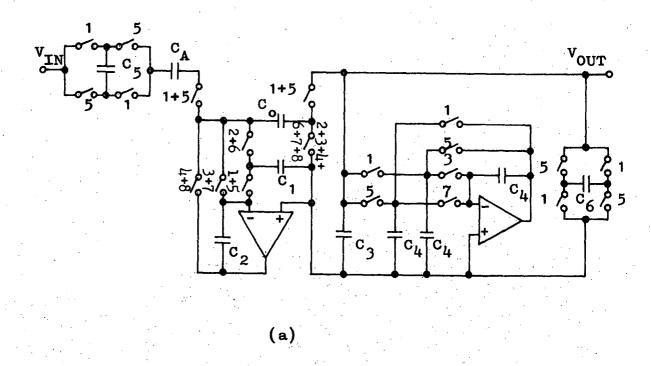

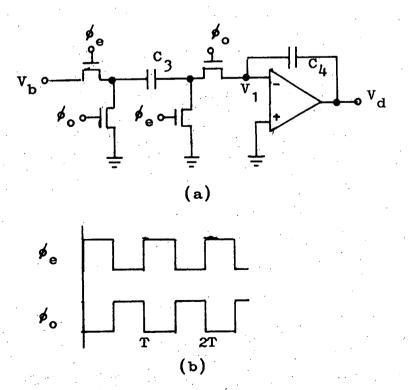

As an example, the two-integrator loop shown in fig. 3:2 has proper switch phasing and thus is free from phase errors. This loop forms an important section in building switched-capacitor ladder filters as discussed in chapter 6. Note that integrator 1 in fig. 3:2 realises the switched-capacitor differential integrator, since capacitor  $C_3$  is charged to the difference between two input voltages,  $V_a$  and  $V_b$ . Using the equivalent circuit method in chapter 2, the input-output relation is determined to be

$$v_{d}^{e} = -\frac{c_{3}}{c_{4}} \frac{z^{-\frac{1}{2}}}{1-z^{-1}} (v_{a}^{o} - v_{b}^{o})$$

(3:12)

From (3:12), it can also be noted that integrator 1 in fig. 3:2 becomes a non-inverting integrator if  $V_{\bf a}$  is grounded.

## 3.2 Effects of Parasitic Capacitances

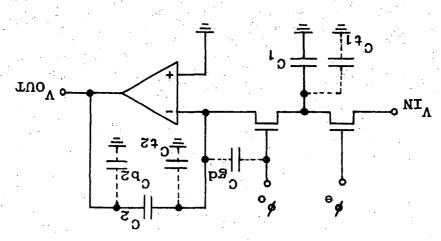

Another deviation of the SCI from ideal behaviour could be contributed by parasitic capacitances as shown in fig. 3:3 with the SCI of fig. 3:1(b) drawn in its MOS implementation. The gate-to-diffusion overlap capacitance, such as  $C_{\rm gd}$  feeds a portion of the clock signal,  $\phi_0$  onto the output. The effect of this feedthrough is to produce a dc offset voltage at the output of the integrator. Self-aligned MOS technologies with small overlap capacitances can be used to greatly reduce this effect. [5] Also, if CMOS switches are used, the positive rising and negative falling edges causing feedthrough are nearly matched and almost exactly cancelled. [6]

Another technique to overcome clock feedthrough is by adding a network to the positive input of the OA to cancel the signal injected by clock feedthrough at the negative terminal. [7] The cancellation, however, is dependent upon matching of the switches involved and assumes infinite common mode rejection ratio (CMRR) of the OA besides requiring double the total amount of capacitances.

Parasitic capacitances  $C_{t2}$  and  $C_{b2}$  from the top and bottom plates, respectively, of the integrating capacitor  $C_2$ , have no effect on circuit operation. This is due to their being always connected to virtual ground and a voltage source respectively. The top plate of the capacitor, which has lower parasitics, needs to be connected to the negative input of the OA in order not to impose stringent requirement on the OA low frequency gain.

The parasitic capacitance,  $^{\text{C}}_{\text{tl}}$ , from the top plate of capacitor  $^{\text{C}}_{\text{l}}$ , includes parasitic capacitances from the source or drain of the switches connected to  $^{\text{C}}_{\text{l}}$ . It is charged to  $^{\text{V}}_{\text{IN}}$  and discharged onto the integrating

capacitor. Thus error is introduced into the integrator gain. To attain a required accuracy, large C<sub>1</sub> is needed which increases the required circuit area. Furthermore, the parasitic capacitance is non-linear, hence, unacceptable harmonic distortion may be generated.

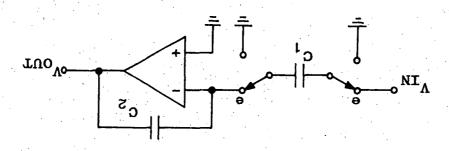

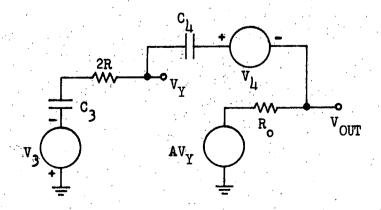

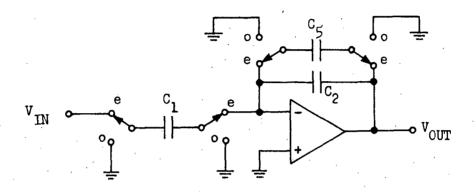

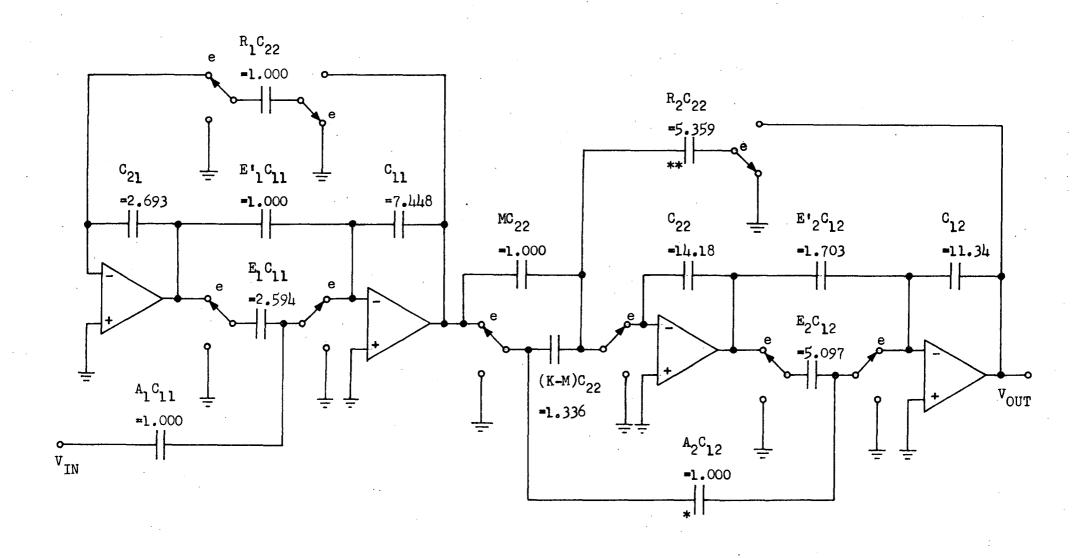

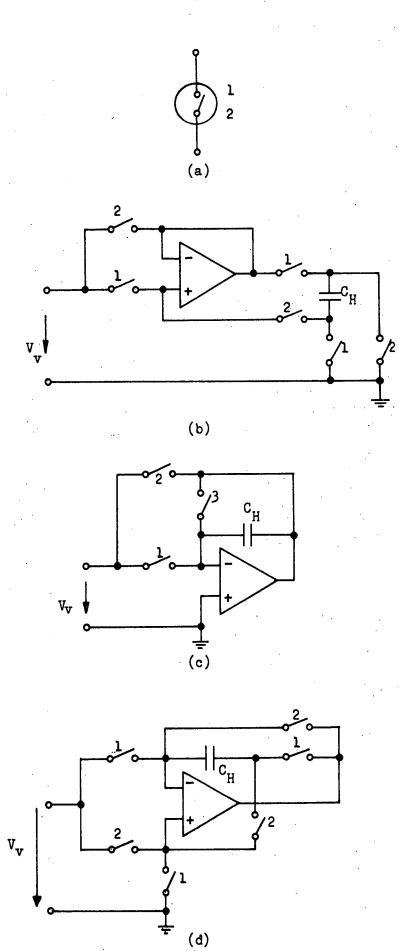

The non-inverting integrator 1, with  $V_a$  grounded in fig. 3:2, however, is free from effects of parasitic capacitances. The top plate parasitic of  $C_3$  is switched between ground and virtual ground while the bottom plate parasitic capacitance is switched between a voltage source and ground. The same arrangement is used to obtain parasitic-insensitive inverting SCI as shown in fig. 3:4.[8] This circuit realises the same transfer function (3:6) as the series-switched integrator of fig. 3:1(c) except that the latter is sensitive to parasitics.

Eqn. (3:6) shows that this inverting integrator is delay free, and thus, in order to realise the same function as provided by the loop in fig. 3:2, it is necessary to connect it with a non-inverting integrator having one cycle delay as shown in fig. 3:5.[9] On the average through the loop there will still be half-cycle delay per integrator as required to realise the LDI transformation. Integrator 1 in fig. 3:5 also implements a switched-capacitor differential integrator. It remains parasitic insensitive since the bottom plate parasitic capacitance of capacitor  $C_3$  is now switched between voltage sources. The input-output relation of the integrator is

$$V_d^e = -\frac{C_3}{C_4} \frac{1}{1-z^{-1}} (z^{-\frac{1}{2}} V_a^o - z^{-1} V_b^e)$$

(3:13)

Although the parasitic-insensitive integrators above provide efficient and practical solutions to many SCF problems, there are certain advantages in keeping the toggle-switched topology as in fig. 3:1(b). As an example,

Fig. 3:3 MOS implementation of the toggle-switched integrator with parasitic capacitances.

Fig. 3:4 Parasitic-insensitive inverting integrator.

Fig. 3:5 Parasitic-insensitive two-integrator loop.

the toggle-switched integrator does not have a continuous path between input and output at any time. Thus other ways of overcoming the top-plate parasitics in the toggle-switched integrator have been suggested.

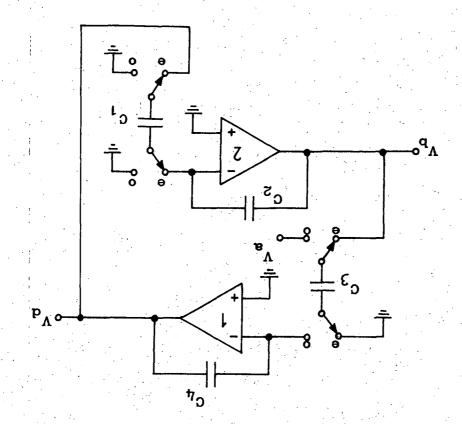

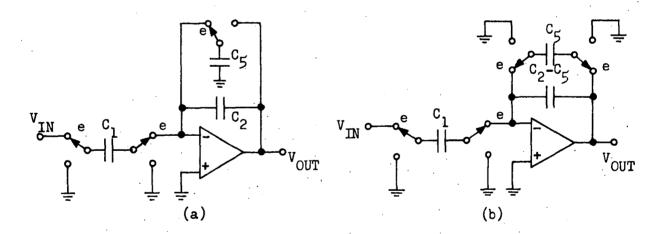

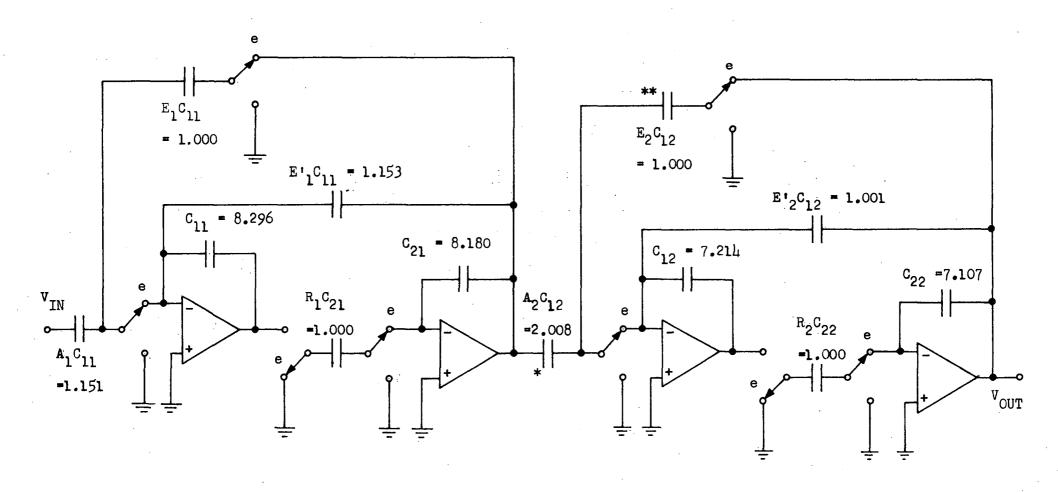

One such method is through the use of the parasitic compensated integrator shown in fig. 3:6(a) together with the relevant parasitic capacitances,  $^{\text{C}}_{\text{tl}}$  and  $^{\text{C}}_{\text{t2}}$ . The equivalent circuit of the integrator is shown in fig. 3:6(b). Assuming linear parasitic capacitances, the transfer function is given by

Heo =

$$-\frac{2C_1(2C_1 + C_{t2})z^{-\frac{1}{2}}}{C_2(4C_1 + C_{t1} + C_{t2})(1 - z^{-1})}$$

(3:14)

The same transfer functions as in (2:24) are obtained if  $^{C}_{t1}$ =  $^{C}_{t2}$ . This is possible if the routings associated with nodes 1 and 2 are made equal and equal-sized switches are used.[10] The same is true when non-linear parasitic capacitances are considered as shown in [11].

The matching condition may be difficult to ensure in practice. Nevertheless this method is better than predistorting the capacitor  $C_1$  in fig. 3:1(b) to compensate for the top plate parasitic capacitance. The compensated integrator of fig. 3:6(a), however, requires two capacitors for  $C_1$ , each having double the value of  $C_1$  in fig. 3:1(b). The parasitic compensated non-inverting integrator is obtained by changing the phasing of the switches connected to nodes 1 and 2 of the integrator in fig. 3:6(a). It differs from the non-inverting integrator in fig. 3:2 in that it produces an extra half-cycle delay.

## 3.3 Frequency Limitations

Non-ideal switches and OA used in the SCI are further causes of deviation in its behaviour. Their effects, however, are mainly frequency

Fig. 3:6(a) Parasitic-compensated inverting integrator.

(b) Its equivalent circuit.

Fig. 3:7 Equivalent circuit for a charging half-period.

Fig. 3:8 Equivalent circuit for a discharging half-period.

dependent. A range of frequencies can thus be found where the effects of these non-idealities are negligible.

Low frequency use of the SCI is limited by leakage currents from the switch source and drain to the substrate during its off-state. These cause a dc voltage drift which shows up as a component of the output voltage offset. This offset can be reduced by limiting the usable clock frequency to a few hundred Hertz. Other major offset contributions due to clock feedthrough and offset of the OA have also to be reduced for low frequency applications. The dc input offset of the OA can be reduced by employing auto-zero techniques. [12]

The switch on-resistance, R, on the other hand, has an effect on the maximum allowable clock frequency. Its effects have to be analysed together with that of the OA non-idealities due to their interaction.[13] The OA is assumed to have a finite low frequency gain, A and a single pole, with output resistance, R<sub>O</sub>. This represents a practical model for the OA with its gain function given by

$$A(s) = -\frac{A_0 p_0}{s + p_0}$$

(3:15)

where  $A_0p_0 = \omega_t = 2 \pi f_t$  is the unity-gain bandwidth of the OA.

The analysis involves considering the charging and discharging transients of the integrator stages. In fig. 3:5, during the even half period, amplifier 2 is charging capacitor  $C_3$ . If the integrating capacitor  $C_2$  is assumed to have been fully charged to attain a voltage  $V_2$  across it, then the equivalent circuit in fig. 3:7 can be used. The output is given by

$$V_{\text{out}} = -\frac{A_0 p_0 V_2}{(R_0 + 2R)^C_{3} s^2 + [1 + (R_0 + 2R) p_0 C_3 + 2RA_0 p_0 C_3] s + p_0 + A_0 p_0}$$

(3:16)

The final value of  $V_{out}$  is

$$v_{out} \mid_{t \to \infty} = -\frac{A_0}{1 + A_0} v_2$$

(3:17)

Large  $A_{\rm O}$  is thus required to ensure complete charge transfer. If  $A_{\rm O}$  is large, then  $P_{\rm O}$  and the second term of the coefficient of s in (3:16) can be neglected.

The time V<sub>out</sub> takes to reach an acceptable percentage of its final value can be estimated from the poles of (3:16). For complex poles, their real part can be taken as the controlling time constant. In case of real poles, the one with the lowest absolute value can usually be taken as the controlling term. These estimates give an indication the minimum length of time required for the even half period and thus the maximum clock frequency for the integrator.

During the odd half period in fig. 3:5, capacitor  $^{\rm C}_3$  is now discharged through the following amplifier 1. If  $^{\rm V}_a$  is grounded, the equivalent circuit for the discharging transient is given in fig. 3:8, where  $^{\rm V}_3$  is nearly equal to the final value in (3:17). The output, in this case, is given by, (neglecting  $^{\rm P}_0$  in (3:15)),

$$V_{\text{out}} = -\frac{(C_3/C_4)(R_0C_4s^2 - A_0p_0)V_3 + [R_0C_3s^2 + 2RC_3A_0p_0s + A_0p_0]V_4}{(R_0 + 2R)C_3s^2 + (1 + C_3/C_4 + 2RA_0p_0C_3)s + A_0p_0}$$

(3:18)

Thus an indication for the minimum length of time required for the odd half period can similarly be obtained.

It should be noted that in fig. 3:5, the charging and discharging of  $C_1$  occurs in the same even half period as the charging of  $C_3$ . Hence, in actual fact, for this case, the time for the even half period need to be longer than that estimated using (3:16). The switch on-resistance can be

reduced to  $1k\Omega$  or less by increasing the width-to-length ratio of the switching transistors but leakage will increase. A choice can thus be made between the two extremes depending on whether high or low frequency application is desired.

In practice, the capacitance level is usually low enough for the effects of switch on-resistance to be neglected, if the frequencies of interest are not too high. As an example, using capacitor values  $C_3 = 10 \mathrm{pF}$ ,  $C_4 = 30 \mathrm{pF}$  and pessimistic values for  $R = R_0 = 5 \mathrm{k}\Omega$ ,  $A_0 = 500$  and  $p_0 = 2 \mathrm{II}(1 \mathrm{kHz})$  in fig. 3:8, eqn (3:18) gives an estimate that the maximum allowable clock frequency is about 230kHz for  $V_{\mathrm{out}}$  to reach 99.5 percent of its final value. If R is made zero, the maximum allowable clock frequency is estimated to be about 245kHz, showing little variation over the whole range of R. Thus keeping the clock frequency below 230kHz, the effects of the switch on-resistance can be neglected.

In this case, the effects of the OA finite bandwidth,  $\omega_{\rm t}$  may become dominant. The transfer function of the SCI, incorporating these effects, can be derived through time domain analysis assuming input signals which are step functions as shown in Appendix A. In the loop of fig. 3:5 with  $V_a$  grounded, OA 1 receives a step input at the beginning of the o clock phase and thus  $V_b$  is assumed to be sampled at this instant.  $V_d$  is sampled at the beginning of the e clock phase and it is assumed to be constant during this phase while being received by OA 2. Under these conditions transfer functions  $H_1^{OE}$  and  $H_2^{OE}$  of integrators 1 and 2, respectively, are given by (let  $C_1 = C_3$ ,  $C_2 = C_4$  for convenience),

$$H_1^{\text{oe}} = -H_2^{\text{eo}} = \frac{C_1}{C_2} \frac{z^{-\frac{1}{2}}}{1-z^{-1}} \frac{1 - [1-Kz^{-1}(1-\exp(-k_2))]\exp(-k_1)}{1 - Kz^{-1}\exp(-k_1-k_2)}$$

(3:19)

where

$$k_1 = Kk_2, k_2 = \omega_t T/2, K = \frac{C_2}{C_1 + C_2}$$

(3:20)

If an integrator has more than one input capacitor, then the sum of all the input capacitors replaces  $^{\rm c}_1$  in (3:19). However, the signals into these capacitors must be step functions, as assumed in the analysis. If the sum of the input capacitors is smaller in value than the integrating capacitor, and  $f_{\rm t}/f_{\rm c}$  >5, (3:19) shows that the effects of the OA bandwidth are negligible. [14]

The transfer function of the SCI, incorporating the effects of only the finite gain, Ao can be obtained using the equivalent circuit analysis as in fig. 2:10, with the OA replaced by voltage controlled voltage sources. For the inverting integrator in fig. 3:5, the transfer function is

$$H^{ee} = -\frac{C_1}{C_2} \frac{1}{1-z} - 1 \frac{1}{1+\frac{1}{A_0}(1+\frac{C_1}{C_2} \frac{1}{1-z}-1)}$$

(3:21)

The same error expression as in the bracket in (3:21) is obtained for the non-inverting integrator in fig. 3:5. The error consists of the magnitude error,  $M(\omega)$  and the phase error,  $\Theta(\omega)$ , where [14]

$$M(\omega) = -\frac{1}{A_0} \left(1 + \frac{C_1}{2C_2}\right)$$

$$\Theta(\omega) = \frac{C_1}{C_2} \frac{1}{2A_0 \tan (\omega T/2)}$$

(3:22)

The phase error requires the clock frequency to be low compared to the signal frequencies. Otherwise A<sub>O</sub> has to be made large to keep the error below an acceptable level.

The OA slew rate and settling time are other factors which limit the highest possible clock frequency. The amplifier needs to respond to change

in signal which occurs each clock cycle. The amount of change is dependent on the ratio of the clock to passband frequencies. Knowing the maximum instantaneous change in the signal, and given the OA slew rate and settling time, the maximum clock frequency can be determined.

## 3.4 Noise Considerations

Noise is another limiting factor in the use of the SCI. The important sources of noise in SCI are the thermal noise in the MOS transistor switches, the wideband thermal noise and the 1/f noise of the OA.[15] The thermal noise in the switches is due to their on-resistances. The total input-referred rms noise within the bandwidth of the integrator is approximately kT/C where C is the integrating capacitance and kT is the thermal voltage.[16] This is assuming the clock frequency is much larger than the frequencies of interest. Thus C needs to be large to reduce this noise. Power supply noise coupled into the integrating node by parasitic capacitance also require that C be large for good power supply rejection ratio (PSRR).[17] However, circuit area consideration poses a limit to the size of C.

The wideband noise of the OA has bandwidth greater than the clock rate of the SCI. Hence a portion of the high frequency components of this noise is aliased into the passband when the integrators are cascaded. [18] A low level of noise output at frequencies beyond the  $f_t$  of the OA can be achieved by using one or two stages OA without an output stage.  $f_t$  of the OA in excess of the settling requirements, as dictated by clock frequencies, has also to be avoided in order to reduce the effect of this noise.

1/f noise is concentrated at low frequencies and arises because of the surface behaviour in the channel of MOS transistors. Its magnitude is dependent on the process used, the design of the OA, and the size of input

transistors used in the OA. This noise is often the dominant source in low frequency applications. Approaches which involved modifying the channel of the transistors have been used in the past to reduce the  $1/_{\rm f}$  noise. Two other approaches, using circuit techniques, have also been suggested.

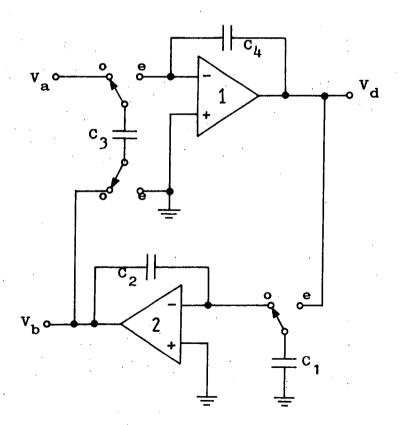

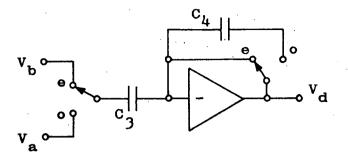

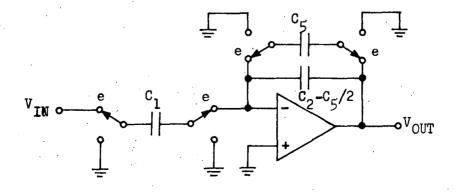

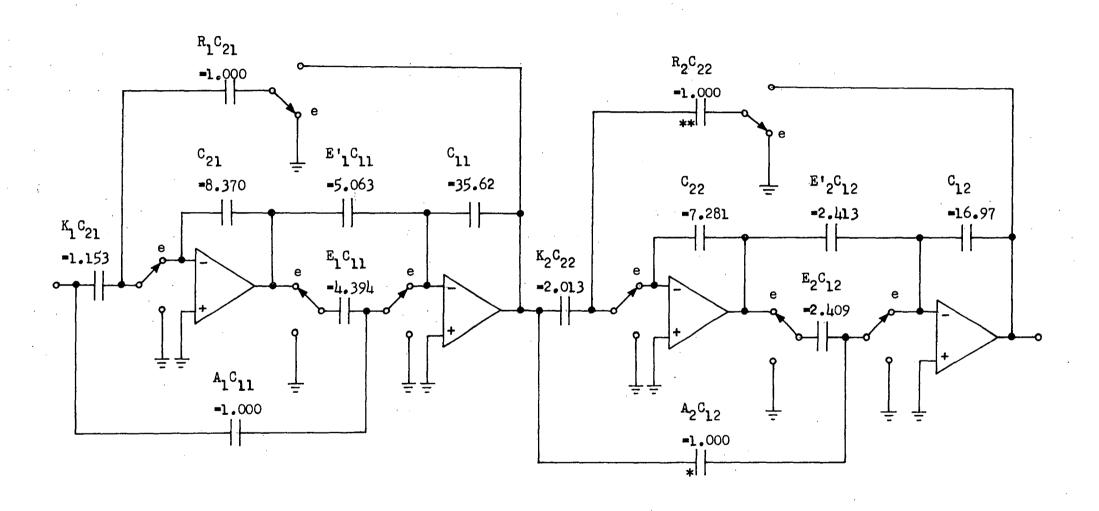

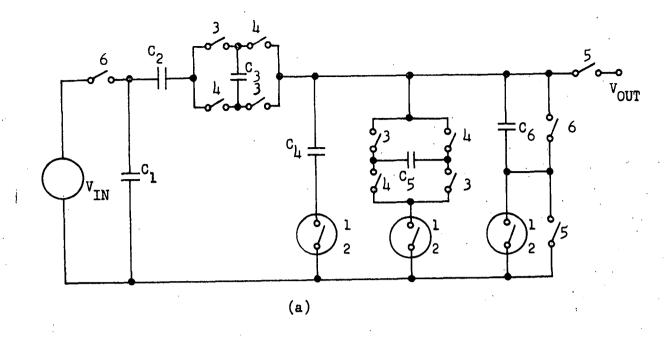

One method is through using the correlated double sampling (CDS) technique. This involves replacing the SCI such as integrator 1 in fig. 3:5 by the integrator shown in fig. 3:9. The OA is replaced by a very high gain inverter, ensuring virtual ground at the amplifier input. Thus the same stray insensitive function as for integrator 1 in fig. 3:5 is obtainable with the advantage that it is also insensitive to offset of the amplifier and to slow variation with respect to the clock frequency. [19] The effect of 1/f noise component generated in the amplifier will now be reduced.

An inverter with a lower noise factor than the OA can also be used to reduce the wideband thermal noise component as well. Thus, in this case, the thermal noise of the switches becomes the dominant noise source. The signal output of the integrator, however, is now only available during the odd half period. Hence an extra clock phase is necessary for its use in the loop as in fig. 3:5.

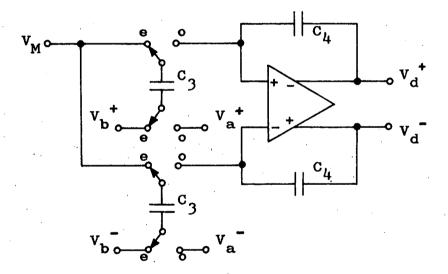

Another method of 1/f noise reduction is by using chopper stabilisation technique. This involves modulating the noise using a chopping square wave causing the 1/f noise component to be shifted to the odd harmonic frequencies of the chopper. If the chopper frequency is much higher than the signal bandwidth, then 1/f noise in the signal band will be greatly reduced. The maximum reduction occurs when the chopper frequency equals  $f_{c/2}$ .

Fig. 3:9 Correlated double sampling differential integrator.

Fig. 3:10 Fully differential switched-capacitor integrator.

The chopper circuitry is amenable for incorporation in an OA with differential output configuration such as for the fully differential SCI shown in fig. 3:10.[20] V<sub>M</sub> sets the common mode voltage at the OA input. This configuration doubles the effective signal swing, thus increasing the dynamic range further. It also reduces clock feedthrough and has good PSRR. However, the circuitry is more complex and a differential to single-ended conversion may be necessary in some applications.

These techniques enable the dynamic range of SCF to be extended beyond 100dB.[20] However, without these modifications, dynamic range of up to 90dB is still possible. This is usually sufficient in many applications.

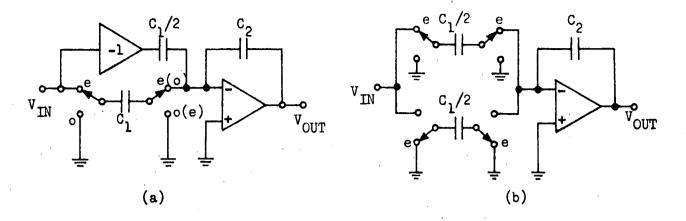

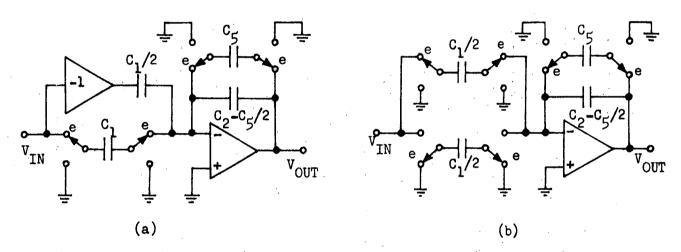

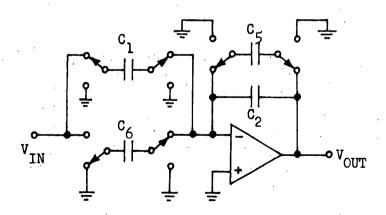

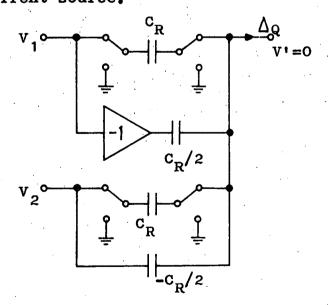

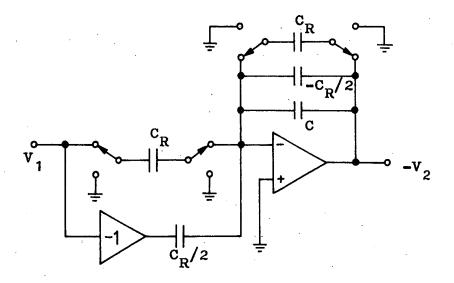

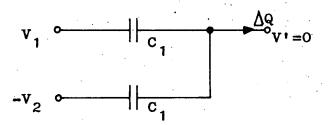

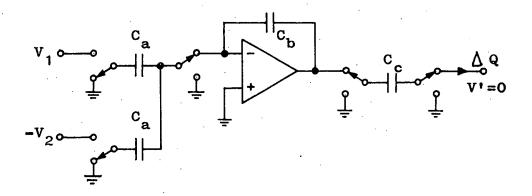

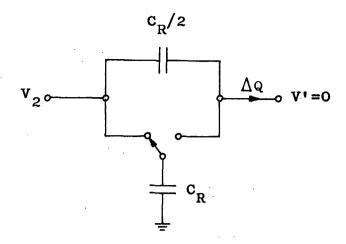

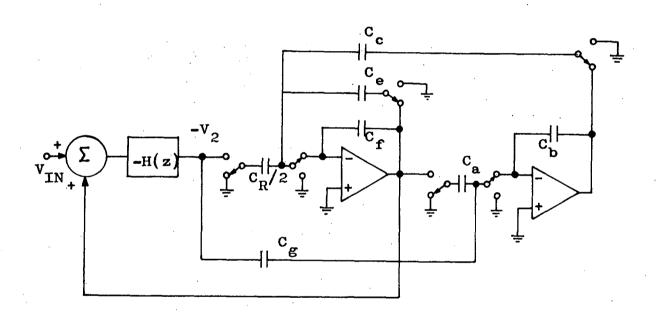

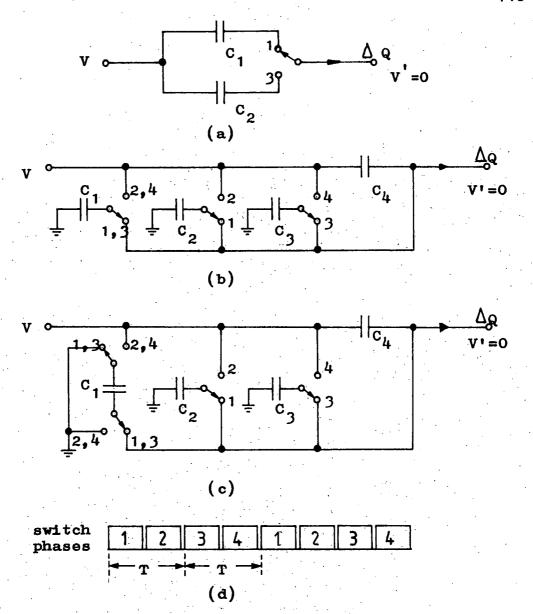

## 3.5 Damped Switched-capacitor Integrators